|

|

PDF Si5341-40-RM Data sheet ( Hoja de datos )

| Número de pieza | Si5341-40-RM | |

| Descripción | CLOCK GENERATOR | |

| Fabricantes | Silicon Laboratories | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de Si5341-40-RM (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

U LTRA L OW J ITTER, A NY- F REQUENCY, A NY- O UTPUT

CLOCK GENERATOR

Si5341, Si5340

FAMILY REFERENCE MANUAL

Rev. 1.1 9/15

Copyright © 2015 by Silicon Laboratories

Si5341-40-RM

1 page

LIST OF TABLES

Si5341-40-RM

Table 1. Product Selection Guide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Table 2. Reset Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Table 3. NVM Programming Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Table 4. Manual Input Selection Using IN_SEL[1:0] Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 5. Input Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 6. Status Monitor Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 7. Interrupt Mask Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 8. Example of Output Clock Frequency Sequencing Choice . . . . . . . . . . . . . . . . . . . . 20

Table 9. Output Signal Format Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Table 10. Differential Output Voltage Swing (Amplitude) Control Registers . . . . . . . . . . . . . . 23

Table 11. Settings for LVDS, LVPECL, and HCSL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 12. Output Impedance and Drive Strength Selections . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 13. LVCMOS Drive Strength Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 14. LVCMOS Output Polarity Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Table 15. Output Enable/Disable Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 16. Output Driver Disable State Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 17. Synchronous Disable Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Table 18. Delay Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Table 19. Output Crosspoint Control Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Table 20. I2C/SPI Register Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Table 21. SPI Command Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 22. Recommended Crystals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Table 23. Recommended Oscillator Suppliers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 24. Power Management Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Table 25. Register Map Paging Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 26. Registers for OUT1,2,3,4,5,6,7,8,9 as per above for OUT0 . . . . . . . . . . . . . . . . . . 70

Table 27. R Dividers for Outputs 1,2,3,4,5,6,7,8,9 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Table 28. N1, N2, N3 Numerator and Denominators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Table 29. Frequency Step Word for N1, N2, N3, N4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Table 30. Registers for OUT1,2,3 as per OUT0 Above. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Table 31. R Dividers for Output 1,2,3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Table 32. N Dividers for N1, N2, N3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Table 33. Frequency Step Word for N1, N2, N3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Table 34. Output Differential Common Mode Voltage Settings. . . . . . . . . . . . . . . . . . . . . . . 109

Table 35. Typical Differential Amplitudes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Rev. 1.1

5

5 Page

3. Power-Up and Initialization

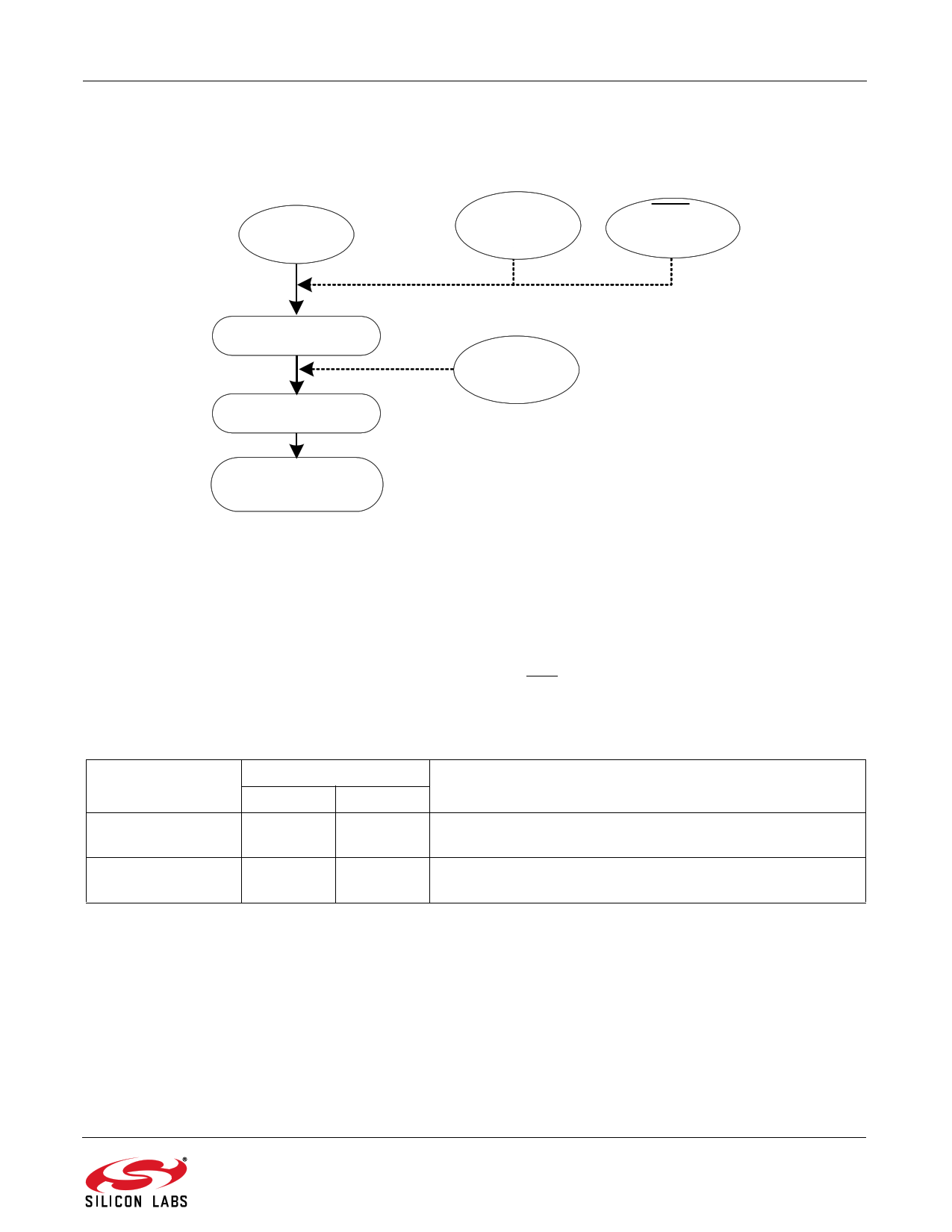

Figure 4 shows the power-up and initialization sequence Figure 4.

Power-Up

Hard Reset

bit asserted

Si5341-40-RM

RST

pin asserted

NVM download

Initialization

Soft Reset

bit asserted

Serial interface

ready

Figure 4. Power-Up and Initialization

3.1. Reset and Initialization

Once power is applied, the device begins an initialization period where it downloads default register values and

configuration data from NVM and performs other initialization tasks. Communicating with the device through the

serial interface is possible once this initialization period is complete. No clocks will be generated until the

initialization is done. There are two types of resets available. A hard reset is functionally similar to a device power-

up. All registers will be restored to the values stored in NVM, and all circuits will be restored to their initial state

including the serial interface. A hard reset is initiated using the RST pin or by asserting the hard reset bit. A soft

reset bypasses the NVM download. It is simply used to initiate register configuration changes.

Register Name

HARD_RST

SOFT_RST

Table 2. Reset Registers

Hex Address [Bit Field]

Function

Si5341

Si5340

001E[1]

001E[1] Performs the same function as power cycling the device. All

registers will be restored to their default values.

001C[0]

001C[0] Performs a soft reset. Resets the device while it does not re-

download the register configuration from NVM.

The Si541/40 is fully configurable using the serial interface (I2C or SPI). At power up the device downloads its

default register values from internal non-volatile memory (NVM). Application specific default configurations can be

written into NVM allowing the device to generate specific clock frequencies at power-up. Writing default values to

NVM is in-circuit programmable with normal operating power supply voltages applied to its VDD (1.8V) and VDDA

(3.3 V) pins.

Rev. 1.1

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet Si5341-40-RM.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| Si5341-40-RM | CLOCK GENERATOR | Silicon Laboratories |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |