|

|

PDF A3S28D40JTP Data sheet ( Hoja de datos )

| Número de pieza | A3S28D40JTP | |

| Descripción | 128M Double Data Rate Synchronous DRAM | |

| Fabricantes | Zentel | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de A3S28D40JTP (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

A3S28D40JTP

128M Double Data Rate Synchronous DRAM

128Mb DDR SDRAM Specification

A3S28D40JTP

Zentel Electronics Corp.

Revision 1.0

Oct., 2013

1 page

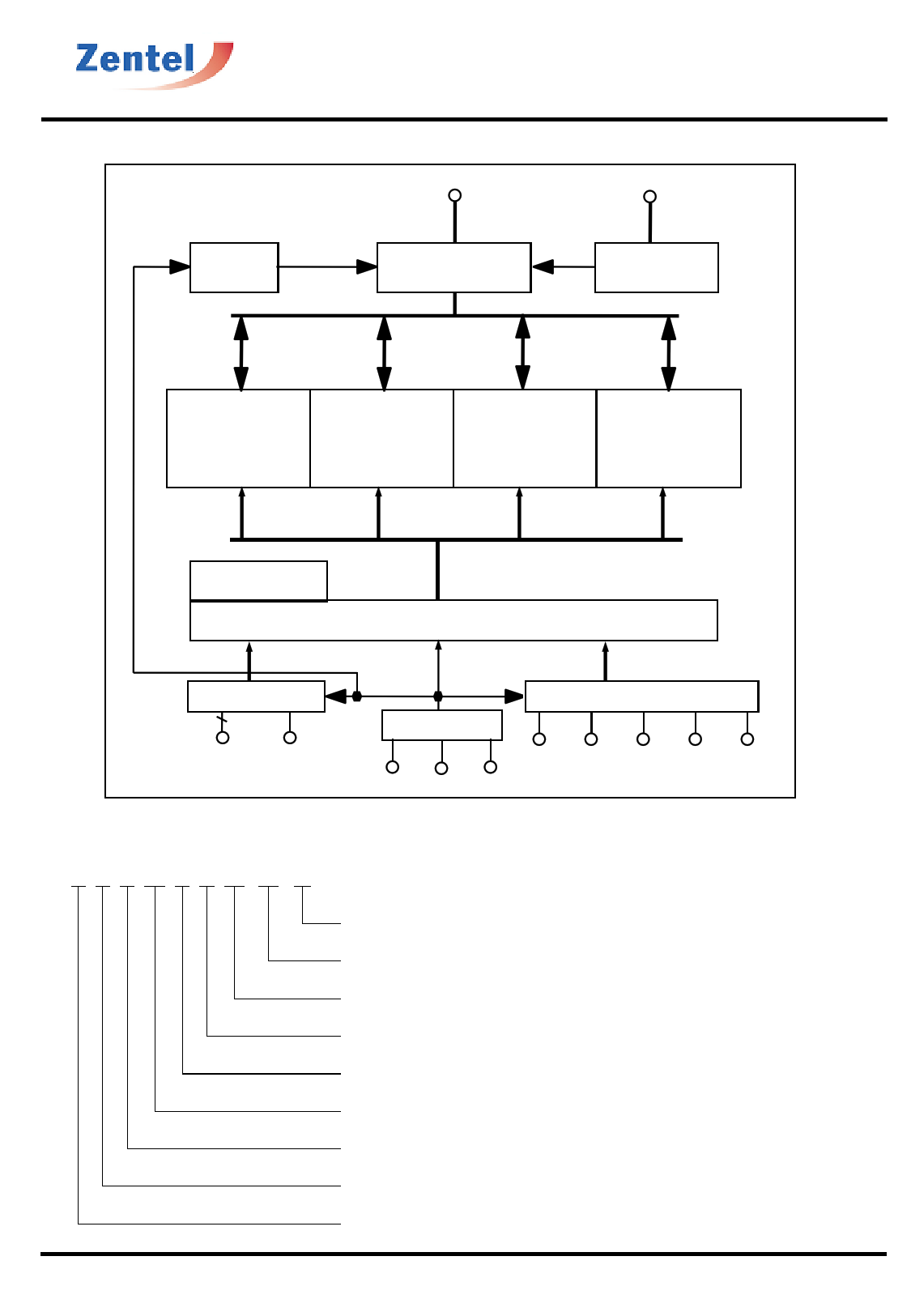

BLOCK DIAGRAM

A3S28D40JTP

DLL

A3S28D40JTP

128M Double Data Rate Synchronous DRAM

DQ0 - 15

UDQS, LDQS

I/O Buffer

DQS Buffer

Memory

Array

Bank #0

Memory

Array

Bank #1

Memory

Array

Bank #2

Memory

Array

Bank #3

Mode Register

Control Circuitry

Address Buffer

A0-11 BA0,1

Type Designation Code

A 3 S 28 D 4 0J TP - 50

Clock Buffer

Control Signal Buffer

/CS /RAS /CAS /WE UDM,

CLK /CLK CKE

LDM

This rule is applied to only Synchronous DRAM family.

Speed

50: 200MHz@CL=3, 166MHz@CL=2.5, and 133MHz@CL=2

Package Type TP: TSOP II

Die Version

0J: Version 0J

I/O Configuration 4: x16

Classification D: DDR Synchronous DRAM

Density

28: 128Mb

Interface

S: SSTL_2

Product Line 3: DRAM

Zentel Memory

Revision 1.0

Page 4/ 39

Oct., 2013

5 Page

A3S28D40JTP

128M Double Data Rate Synchronous DRAM

FUNCTION TRUTH TABLE (continued)

Current State /CS /RAS /CAS /WE Address

Command

PRE-

H X X XX

DESEL

CHARGING L H H H X

NOP

L H H L BA

TERM

L H L X BA, CA, A10 READ / WRITE

L L H H BA, RA

ACT

L L H L BA, A10

PRE / PREA

L L L HX

REFA

LL

L L Op-Code, Mode- MRS

Add

ROW

ACTIVATING

H

L

L

X

H

H

X XX

H HX

H L BA

DESEL

NOP

TERM

L H L X BA, CA, A10 READ / WRITE

L L H H BA, RA

ACT

L L H L BA, A10

PRE / PREA

L L L HX

REFA

LL

L L Op-Code, Mode- MRS

Add

WRITE RE-

COVERING

H

L

L

X

H

H

X XX

H HX

H L BA

DESEL

NOP

TERM

L H L X BA, CA, A10 READ / WRITE

L L H H BA, RA

ACT

L L H L BA, A10

PRE / PREA

L L L HX

REFA

LL

Op-Code, Mode-

L L Add

MRS

Action

NOP (Idle after tRP)

NOP (Idle after tRP)

ILLEGAL

ILLEGAL

ILLEGAL

NOP (Idle after tRP)

ILLEGAL

ILLEGAL

NOP (Row Active after tRCD)

NOP (Row Active after tRCD)

ILLEGAL

ILLEGAL

ILLEGAL

ILLEGAL

ILLEGAL

ILLEGAL

NOP

NOP

ILLEGAL

ILLEGAL

ILLEGAL

ILLEGAL

ILLEGAL

ILLEGAL

Notes

2

2

2

4

2

2

2

2

2

2

2

2

Revision 1.0

Page 10/ 39

Oct., 2013

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet A3S28D40JTP.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| A3S28D40JTP | 128M Double Data Rate Synchronous DRAM | Zentel |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |