|

|

PDF GAL20VP8 Data sheet ( Hoja de datos )

| Número de pieza | GAL20VP8 | |

| Descripción | High-Speed E2CMOS PLD Generic Array Logic | |

| Fabricantes | Lattice Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de GAL20VP8 (archivo pdf) en la parte inferior de esta página. Total 17 Páginas | ||

|

No Preview Available !

GAL20VP8

High-Speed E2CMOS PLD

Generic Array Logic™

Features

• HIGH DRIVE E2CMOS® GAL® DEVICE

— TTL Compatible 64 mA Output Drive

— 15 ns Maximum Propagation Delay

— Fmax = 80 MHz

— 10 ns Maximum from Clock Input to Data Output

— UltraMOS® Advanced CMOS Technology

• ENHANCED INPUT AND OUTPUT FEATURES

— Schmitt Trigger Inputs

— Programmable Open-Drain or Totem-Pole Outputs

— Active Pull-Ups on All Inputs and I/O pins

• E2 CELL TECHNOLOGY

— Reconfigurable Logic

— Reprogrammable Cells

— 100% Tested/100% Yields

— High Speed Electrical Erasure (<100ms)

— 20 Year Data Retention

• EIGHT OUTPUT LOGIC MACROCELLS

— Maximum Flexibility for Complex Logic Designs

— Programmable Output Polarity

— Architecturally Compatible with Standard GAL20V8

• PRELOAD AND POWER-ON RESET OF ALL REGISTERS

— 100% Functional Testability

• APPLICATIONS INCLUDE:

— Ideal for Bus Control & Bus Arbitration Logic

— Bus Address Decode Logic

— Memory Address, Data and Control Circuits

— DMA Control

• ELECTRONIC SIGNATURE FOR IDENTIFICATION

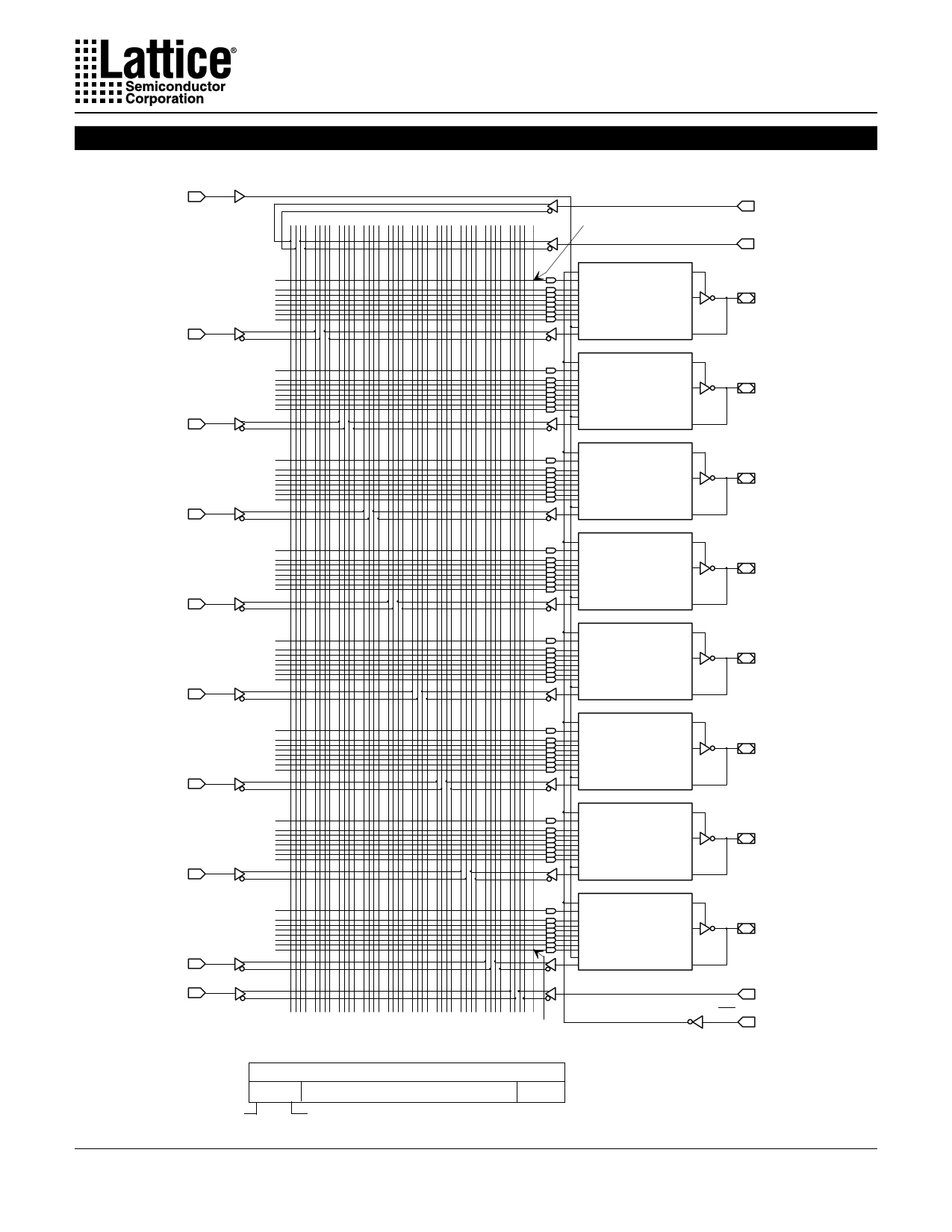

Functional Block Diagram

I/CLK

IMUX

CLK

8 OLMC

I

8 OLMC

I

8 OLMC

I

8 OLMC

I

8 OLMC

I

8 OLMC

I

8 OLMC

I

I 8 OLMC

OE

I

IMUX

I

I

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I

I/OE

Description

The GAL20VP8, with 64 mA drive capability and 15 ns maximum

propagation delay time is ideal for Bus and Memory control appli-

cations. The GAL20VP8 is manufactured using Lattice

Semiconductor's advanced E2CMOS process which combines

CMOS with Electrically Erasable (E2) floating gate technology. High

speed erase times (<100ms) allow the devices to be reprogrammed

quickly and efficiently.

System bus and memory interfaces require control logic before

driving the bus or memory interface signals. The GAL20VP8

combines the familiar GAL20V8 architecture with bus drivers as

its outputs. The generic architecture provides maximum design flex-

ibility by allowing the Output Logic Macrocell (OLMC) to be con-

figured by the user. The 64mA output drive eliminates the need for

additional devices to provide bus-driving capability.

Unique test circuitry and reprogrammable cells allow complete AC,

DC, and functional testing during manufacture. As a result,

Lattice Semiconductor delivers 100% field programmability and

functionality of all GAL products. In addition, 100 erase/write cycles

and data retention in excess of 20 years are specified.

Pin Configuration

PLCC

4

I5

2 28 26

25 I/O/Q

I I/O/Q

Vcc 7 GAL20VP8 23 I/O/Q

NC NC

I 9 Top View 21 GND

I I/O/Q

I 11

19 I/O/Q

12 14 16 18

DIP

I/CLK 1

I

24 I

I

I I/O/Q

I GAL I/O/Q

I 20VP8 I/O/Q

Vcc 6

I/O/Q

I 18 GND

I I/O/Q

I I/O/Q

I I/O/Q

I I/O/Q

I/OE 12

13 I

Copyright © 1997 Lattice Semiconductor Corp. All brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject

to change without notice.

LATTICE SEMICONDUCTOR CORP., 5555 Northeast Moore Ct., Hillsboro, Oregon 97124, U.S.A.

Tel. (503) 268-8000; 1-800-LATTICE; FAX (503) 268-8556; http://www.latticesemi.com

December 1997

20vp8_03

1

1 page

Specifications GAL20VP8

Registered Mode Logic Diagram

DIP (PLCC) Package Pinouts

1(2)

0 4 8 12 16 20 24 28 32 36 PTD

2640

24(28)

23(27)

2(3)

0000

0280

OLMC

XOR-2560

AC1-2632

AC2-2706

22(26)

3(4)

0320

0600

OLMC

XOR-2561

AC1-2633

AC2-2707

21(25)

4(5)

0640

0920

OLMC

XOR-2562

AC1-2634

AC2-2708

20(24)

5(6)

7(9)

8(10)

0960

1240

1280

1560

1600

1880

OLMC

XOR-2563

AC1-2635

AC2-2709

OLMC

XOR-2564

AC1-2636

AC2-2710

OLMC

XOR-2565

AC1-2637

AC2-2711

19(23)

17(20)

16(19)

9(11)

1920

2200

OLMC

XOR-2566

AC1-2638

AC2-2712

15(18)

2240

10(12)

11(13)

2520

2703

MSB

64-USER ELECTRONIC SIGNATURE FUSES

2568, 2569, ....

.... 2630, 2631

Byte7 Byte6 ....

.... Byte1 Byte0

LSB

OLMC

XOR-2567

AC1-2639

AC2-2713

14(17)

13(16)

OE

12(14)

SYN-2704

AC0-2705

5

5 Page

Specifications GAL20VP8

AC Switching Characteristics

Over Recommended Operating Conditions

TEST

PARAMETER COND1.

DESCRIPTION

tpd A Input or I/O to Combinational Output

tco A Clock to Output Delay

tcf2 — Clock to Feedback Delay

tsu — Setup Time, Input or Feedback before Clock ↑

th — Hold Time, Input or Feedback after Clock ↑

A Maximum Clock Frequency with

External Feedback, 1/(tsu + tco)

fmax3

A Maximum Clock Frequency with

Internal Feedback, 1/(tsu + tcf)

A Maximum Clock Frequency with

No Feedback

twh — Clock Pulse Duration, High

twl — Clock Pulse Duration, Low

ten B Input or I/O to Output Enabled

B OE to Output Enabled

tdis C Input or I/O to Output Disabled

C OE to Output Disabled

COM

-15

MIN. MAX.

3 15

2 10

— 4.5

8—

0—

55.5 —

80 —

80 —

6—

6—

— 15

— 12

— 15

— 12

COM

-25

UNITS

MIN. MAX.

3 25 ns

2 15 ns

— 10

ns

10 —

ns

0 — ns

40 — MHz

50 — MHz

50 — MHz

10 —

10 —

— 20

— 15

— 20

— 15

ns

ns

ns

ns

ns

ns

1) Refer to Switching Test Conditions section.

2) Calculated from fmax with internal feedback. Refer to fmax Specification section.

3) Refer to fmax Specification section.

Capacitance (TA = 25°C, f = 1.0 MHz)

SYMBOL

PARAMETER

CI Input Capacitance

C I/O Capacitance

I/O

*Characterized but not 100% tested.

MAXIMUM*

10

15

UNITS

pF

pF

TEST CONDITIONS

VCC = 5.0V, VI = 2.0V

V = 5.0V, V = 2.0V

CC I/O

11

11 Page | ||

| Páginas | Total 17 Páginas | |

| PDF Descargar | [ Datasheet GAL20VP8.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| GAL20VP8 | High-Speed E2CMOS PLD Generic Array Logic | Lattice Semiconductor |

| GAL20VP8B-15LJ | High-Speed E2CMOS PLD Generic Array Logic | Lattice Semiconductor |

| GAL20VP8B-15LP | High-Speed E2CMOS PLD Generic Array Logic | Lattice Semiconductor |

| GAL20VP8B-25LJ | High-Speed E2CMOS PLD Generic Array Logic | Lattice Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |