|

|

PDF 7811 Data sheet ( Hoja de datos )

| Número de pieza | 7811 | |

| Descripción | Network Security Processor | |

| Fabricantes | Hi-fn | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de 7811 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

DATA SHEET 7811 Network Security

Processor

1 page

® 7811 Network Security Processor

Figure 45. Read RAM command structure ........................................................ 64

Figure 46. Write RAM command structure ....................................................... 65

Figure 47. Result structures ............................................................................... 66

Figure 48. Base Result Structure ....................................................................... 66

Figure 49. Compression Result Structure .......................................................... 67

Figure 50. MAC Result Structure ...................................................................... 68

Figure 51. Encryption Result Structure.............................................................. 68

Figure 52. Context memory modes.................................................................... 69

Figure 53. Context RAM memory usage in single-size modes.......................... 70

Figure 54. Multi-size mode example ................................................................. 70

Figure 55. Multi-size mode memory allocation algorithm ................................ 71

Figure 56. Number of Sessions in Multi-size mode........................................... 72

Figure 57. Security Engine Data register ........................................................... 74

Figure 58. Security Engine Control register ...................................................... 75

Figure 59. Security Engine Interrupt Status register .......................................... 76

Figure 60. Security Engine Configuration register ............................................ 77

Figure 61. Security Engine Interrupt Enable register......................................... 78

Figure 62. Security Engine Status register......................................................... 79

Figure 63. Security Engine FIFO Status register ............................................... 80

Figure 64. Security Engine FIFO Configuration register................................... 80

Figure 65. Security Engine Command Ring Address register ........................... 82

Figure 66. Security Engine Source Ring Address register ................................. 82

Figure 67. Security Engine Result Ring Address register.................................. 83

Figure 68. Security Engine Dest Ring Address register..................................... 83

Figure 69. Security Engine Status and Control register ..................................... 85

Figure 70. Security Engine Interrupt Enable register......................................... 85

Figure 71. Security Engine DMA Config register ............................................. 87

Figure 72. PCI Address “OR” mask register...................................................... 87

Figure 73. PCI Interrupt register........................................................................ 88

Figure 74. PCI Interrupt Enable register............................................................ 88

Figure 75. MIPS Interrupt register..................................................................... 89

Figure 76. MIPS Interrupt Mask register ........................................................... 89

Figure 77. RNG Enable register ........................................................................ 90

Figure 78. RNG Config register ........................................................................ 90

Figure 79. Decoding of the first prescaler field ................................................. 91

Figure 80. RNG Data register ............................................................................ 91

Figure 81. RNG Status register .......................................................................... 92

Figure 82. MIPS SDRAM1 Address register..................................................... 92

Figure 83. MIPS SDRAM2 Address register..................................................... 93

Figure 84. MIPS Group 1 Address register........................................................ 93

Figure 85. MIPS Group 0 Address register........................................................ 94

Figure 86. MIPS PCI1 Address register............................................................. 94

Figure 87. MIPS PCI2 Address register............................................................. 95

Figure 88. MIPS PCI1 Translation register........................................................ 95

Figure 89. MIPS PCI2 Translation register........................................................ 96

Figure 90. MIPS Config register........................................................................ 98

Figure 91. MIPS Reset register.......................................................................... 99

Figure 92. Revision Number register............................................................... 100

Figure 93. EEPROM data register ................................................................... 100

Figure 94. GPDMA1 Source Address register................................................. 101

Figure 95. GPDMA2 Source Address register................................................. 101

Figure 96. GPDMA1 Dest Address register..................................................... 102

Figure 97. GPDMA2 Dest Address register..................................................... 102

Figure 98. GPDMA1_2 Arbitration register .................................................... 103

DATA SHEET DS-0018-00

Page 5

5 Page

® 7811 Network Security Processor

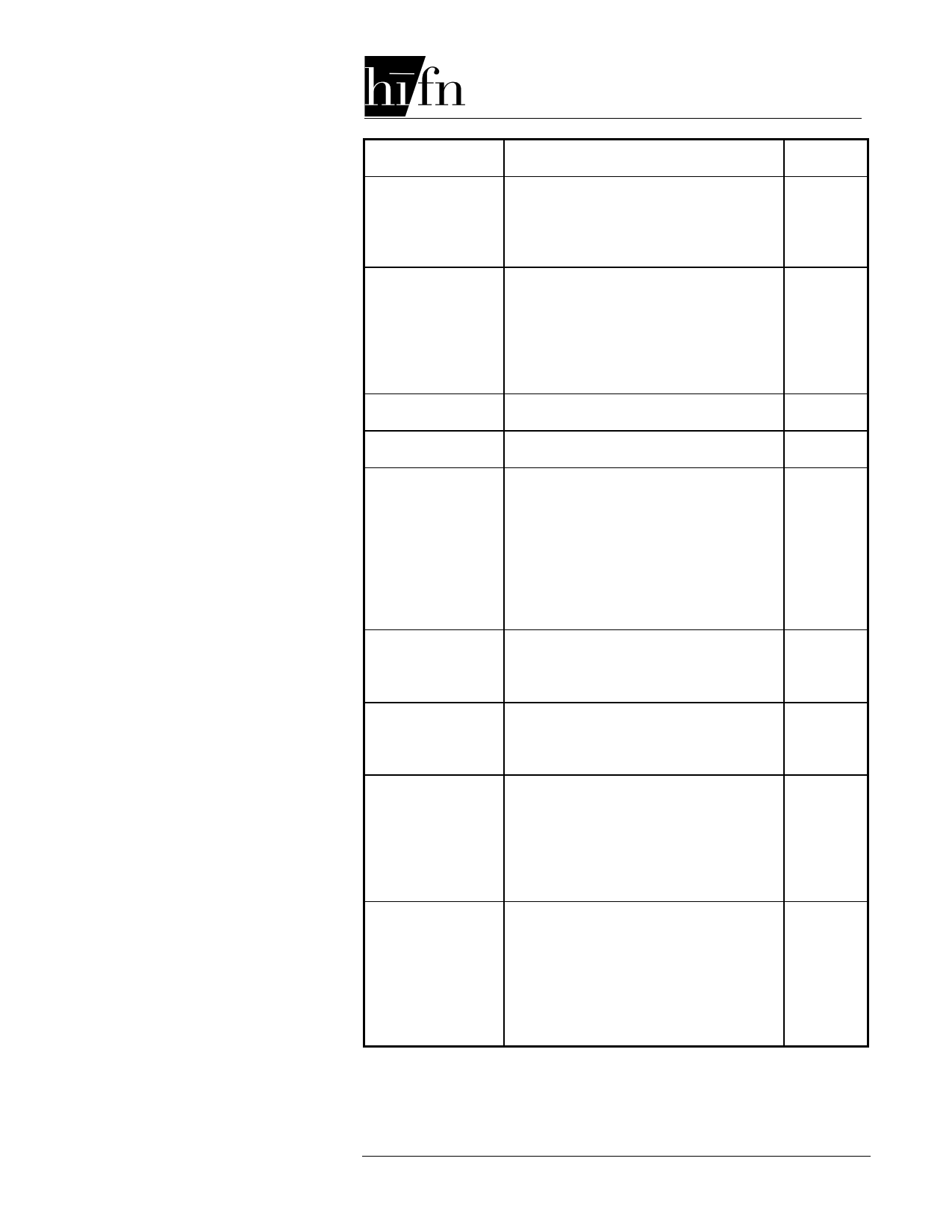

Block

Security Engine

General Purpose

DMA Engines

(GPDMA1-4)

Registers

Random Number

Generator

PCI Interface

Local CPU

Interface

EEPROM Interface

General Purpose

SDRAM

(GPRAM)

Interface

Context SDRAM

Interface

Description

Pipelined compression, encryption,

authentication, and checksum/CRC/LCB

engine with internal DMA engines that

operate independently from the general

purpose DMA engines.

Four identical DMA engines that transfer

commands and data to and from the 7811

subsystem. In protected mode, Only the

source registers of GPDMA 1 and the

destination registers of GPDMA 4 are

accessible to the host; the rest are

controlled by the MIPS CPU.

Configuration, control, and status

registers.

A hardware random-number generator

used in public-key cryptography.

Bus-mastering 33-MHz/32-bit PCI

interface. All features of the 7811 are

available to the host through PCI

accesses, provided the 7811 is in

unprotected mode. In protected mode,

very little of the 7811 can be accessed

through PCI. In addition to being a bus

master, the 7781 is also an efficient PCI

target.

Glueless interface to a MIPS processor.

All features of the 7811 are available to

the MIPS processor through memory-

mapped accesses.

Controls an external 93C46 EEPROM

containing configuration data, including

encryption engine unlock codes that vary

according exportability requirements.

Controls external SDRAM containing

data buffers, general purpose storage, and,

optionally, code for the MIPS processor.

(GPRAM is also called “packet

SDRAM.”) Supports up to 64 MB of

SDRAM in the same chip configurations

as context SDRAM.

Controls external SDRAM containing

per-session compression, encryption, and

authentication state (such as keys and

compression histories). Supports up to 64

MB of SDRAM. Four-bank SDRAM

devices in 8Mx8, 16Mx8, 4Mx16,

8Mx16, and 16Mx16 configurations are

supported.

See

Sections

2.2.1, 6

2.2.2

2.2.3, 8

2.2.4

2.2.5

2.2.6

2.2.7

2.2.8

0

Figure 4. Functional units in the 7811

DATA SHEET DS-0018-00

Page 11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet 7811.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 7810 | 7810 Video Receiver Module | Agere Systems |

| 7810 | 3-terminal 1A positive voltage regulator | SEMTECH |

| 7810F060 | 7810 Video Receiver Module | Agere Systems |

| 7810F115 | 7810 Video Receiver Module | Agere Systems |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |