|

|

PDF GC4116 Data sheet ( Hoja de datos )

| Número de pieza | GC4116 | |

| Descripción | MULTI-STANDARD QUAD DUC CHIP | |

| Fabricantes | ETC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de GC4116 (archivo pdf) en la parte inferior de esta página. Total 57 Páginas | ||

|

No Preview Available !

GRAYCHIP

DSP CHIPS AND SYSTEMS

2185 Park Blvd.,

(650) 323-2955

FAX (650) 323-0206

Palo Alto, CA 94306

GC4116

MULTI-STANDARD

QUAD DUC CHIP

DATA SHEET

REV 1.0

APRIL 27, 2001

This datasheet may be changed without notice.

Graychip reserves the right to make changes in circuit design and/or specifications at any time

without notice. The user is cautioned to verify that datasheets are current before placing orders.

Information provided by Graychip is believed to be accurate and reliable. No responsibility is assumed by

Graychip for its use, nor for any infringement of patents or other rights of third parties which may arise

from its use. No license is granted by implication or otherwise under any patent rights of Graychip.

© Graychip, Inc. All rights reserved 1999-2001

1 page

GC4116 MULTI-STANDARD QUAD DUC CHIP

DATA SHEET REV 1.0

Figure 1:

Figure 2:

Figure 3:

Figure 4:

Figure 5:

Figure 6:

Figure 7:

Figure 8:

Figure 9:

Figure 10:

Figure 11:

Figure 12:

Figure 13:

Figure 14:

Figure 15:

Figure 16:

Figure 17:

Table 1:

Table 2:

Table 3:

Table 4:

Table 5:

Table 6:

Table 7:

Table 8:

Table 9:

Table 10:

Table 11:

Table 12:

Table 13:

Table 14:

Table 15:

Table 16:

LIST OF FIGURES

GC4116 Block Diagram ........................................................................................................................................................ 1

Normal Control I/O Timing .................................................................................................................................................... 3

Edge Write Control Timing .................................................................................................................................................... 3

Serial Input Formats .............................................................................................................................................................. 4

The Up-converter Channel ................................................................................................................................................... 5

Typical PFIR Specifications .................................................................................................................................................. 6

Five Stage CIC Interpolate by N Filter .................................................................................................................................. 7

NCO Circuit ........................................................................................................................................................................... 8

Example NCO Spurs ............................................................................................................................................................. 8

NCO Peak Spur Plot ............................................................................................................................................................. 8

Overall Filter Response ........................................................................................................................................................ 9

Resampler Channel Block Diagram .................................................................................................................................... 11

The Resampler’s Spectral Response ................................................................................................................................. 12

Resampler Serial Output ..................................................................................................................................................... 14

160 Pin Plastic Ball Grid Array (PBGA) Package ............................................................................................................... 19

Reference Design Without the Resampler .......................................................................................................................... 47

Reference Design Using the Resampler ............................................................................................................................. 48

LIST OF TABLES

Sync Modes ........................................................................................................................................................................ 16

Sync Descriptions ............................................................................................................................................................... 16

Mask Revisions ................................................................................................................................................................... 18

GC4116 Pin Out Locations Top View ................................................................................................................................. 20

GLOBAL CONTROL REGISTERS ..................................................................................................................................... 23

Page Assignments .............................................................................................................................................................. 29

IO Control Page Registers (Page 5) .................................................................................................................................... 34

Resampler Control Registers .............................................................................................................................................. 38

Resampler Ratio Page ........................................................................................................................................................ 40

PFIR Coefficient Pages........................................................................................................................................................ 41

Resampler Coefficient Pages (Single filter mode) .............................................................................................................. 42

Absolute Maximum Ratings ................................................................................................................................................ 43

Recommended Operating Conditions ................................................................................................................................. 43

Thermal Data ...................................................................................................................................................................... 43

DC Operating Conditions .................................................................................................................................................... 44

AC Characteristics ............................................................................................................................................................... 45

© 1999−2001 GRAYCHIP,INC.

- iv -

APRIL 27, 2001

This document contains preliminary information which may be changed at any time without notice

5 Page

GC4116 MULTI-STANDARD QUAD DUC CHIP

The interpolated signal is modulated by a sine/cosine

sequence generated by the NCO. In the real output mode the

real part (I-half) of the complex result is saved as the channel

output.

In the complex output mode the CIC interpolation is cut

in half and the NCO/mixer calculates both the I-half and

Q-half of the complex result. In this mode the complex output

sample rate is one-half the clock rate, with the I and Q halves

multiplexed together onto the same output bus.

3.3.1 The Programmable Interpolate By 2

Filter (PFIR)

The input samples are filtered by two stages of

interpolate by 2 filtering before they are interpolated by the

CIC filter. The first stage interpolate by two filter is a 63 tap

filter with programmable 16 bit coefficients. The PFIR will

accept either complex or real input data. If the input samples

are complex, the filter doubles the input rate by inserting

zeroes between each sample, and then low pass filters the

result. If the input samples are real (REAL in address 1 is

set), the filter translates the real samples down by FIN/4,

where FIN is the input sample rate, by multiplying them by the

complex sequence +1, -j, -1, +j, …, and then lowpass filters

the result. This generates a single-sideband modulation of

the real input. Note that in the real input mode the data is

entered as pairs of samples packed into the complex input

word format (see Section 3.2). If double sideband real

upconversion is desired, then the chip should be operated in

the complex mode with the Q-half of each complex pair set

to zero.

The PFIR filter passband must be flat in the region of the

signal of interest, and have the desired out of band rejection

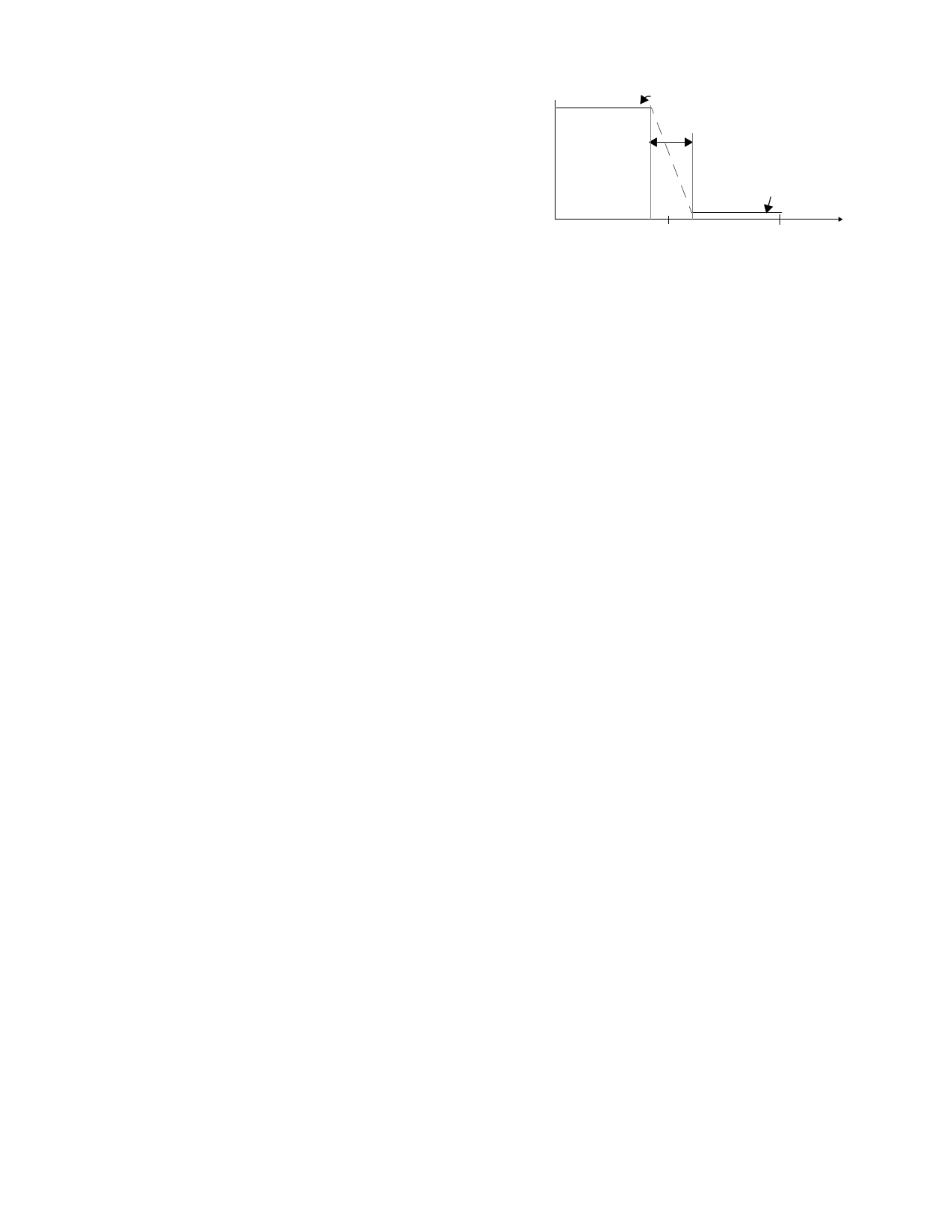

in the region that will contain the interpolation image. Figure

6 illustrates the passband and stopband requirements of the

filter. FIN is the input sample rate to the channel. 2FIN is the

output sample rate of the PFIR. A common use of the PFIR

is to pulse shape digital data. The PFIR will accept QPSK,

O-QPSK, PSK, PAM, OOK, π/4-QPSK, or QAM symbols

and then filter them by the desired pulse shaping filter, which

is commonlt a root-raised-cosine (RRC) filter. The symbols

can be entered directly into the chip at the desired symbol

(baud) rate. The application notes in Section 7 describes

sample filter coefficients sets for common standards

(DAMPS, GSM, IS95, UMTS).

Each channel has its own PFIR coefficient memory, so

the same filter, or a different filter, can be used in each

channel.

The user downloaded filter coefficients are 16 bit 2’s

complement numbers. Unity gain will be achieved through

DATA SHEET REV 1.0

Signal of Interest Passband

0 dB

(Typically 0.25 to 0.4 of FIN)

Power

Narrow transition band

Image Reject Stopband

(Typically starts between

0.6 and 0.75 FIN)

-100 dB

0

FIN/2

FIN Frequency

Figure 6. Typical PFIR Specifications

the filter if the sum of the 63 coefficients is equal to 65536. If

the sum is not 65536, then PFIR will introduce a gain equal

to: PFIR_GAIN = P----F---I--R----_---S---U-----M---- , where PFIR_SUM is the sum of

65536

the 63 coefficients.

The 63 coefficients are identified as coefficients h0

through h62, where h31 is the center tap. The coefficients are

assumed to be symmetric, so only the first 32 coefficients (h0

through h31) are loaded into the chip. A non-symmetric mode

(NO_SYM_PFIR in address 26) allows the user to download

a 32 tap non-symmetric filter as taps h0 through h31. The

newest sample is multiplied by h31 and the oldest is

multiplied by h01.

3.3.2 The Compensating Interpolate by 2

Filter (CFIR)

The second stage filter is a fixed coefficient 31 tap

interpolate by 2 filter. The second stage filter always

interpolates by a factor of two. The second filter has a

passband which is flat (0.01 dB ripple) out to 0.6FIN and

provides over 90dB of image rejection beyond 1.4FIN. The

second filter also compensates for the droop associated with

the CIC interpolation filter described in the next section. The

16 unique coefficients of the symmetric filter are:

-34, -171, -166, 403, 837, -317, -1983, -790,

2820, 3328, -1667, -6589, -4024, 7232, 20602,

26577

The passband of this filter is wide enough to upconvert

digital symbol data with excess bandwidths up to 0.35.

The CFIR output is scaled to have unity gain.

The output rate of the CFIR filter is 4FIN in the complex

input mode and is 2FIN in the real input mode. The CFIR

output rate relative to the clock rate is FCK/N

© 1999−2001 GRAYCHIP,INC.

-6-

APRIL 27, 2001

This document contains preliminary information which may be changed at any time without notice

11 Page | ||

| Páginas | Total 57 Páginas | |

| PDF Descargar | [ Datasheet GC4116.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| GC4114 | 70 MSPS Quad Digital Transmitter | Texas Instruments |

| GC4116 | MULTI-STANDARD QUAD DUC CHIP | ETC |

| GC4116 | Multi-Standard Quad Digital Transmitter (Rev. A) | Texas Instruments |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |