|

|

PDF G2214-208-041DFB2 Data sheet ( Hoja de datos )

| Número de pieza | G2214-208-041DFB2 | |

| Descripción | Transceiver | |

| Fabricantes | GlobespanVirata | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de G2214-208-041DFB2 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

June 25, 2002, Issue 2

Part Numbers

G2216-208-041PF B2 (SDSL 2B1Q)

G2214-208-041DF B2 (SDSL CAP)

G2237-208-041PT B2 (SHDSL/HDSL2)

G2237-208-041PT C1 (SHDSL/HDSL2)

XDSL2TM SDSL, HDSL2, or SHDSL - ILD2

Dual-Channel, Low Power, Programmable

Transceiver with Integrated Framer and Line Drivers

Data Sheet

Overview

The GlobespanVirata® XDSL2™ Digital Subscriber Line

(DSL) chip sets provide low power, high density solutions for

2-wire DSL equipment. These chip sets are fully

programmable and field upgradeable eliminating the risk of

product obsolescence and accelerating the time-to-market for

new network services. The GlobespanVirata® XDSL2™ DSL

chip sets are fully interoperable with multi-vendor DSL chip

set solutions. This interoperability enables dynamic

interworking of multiple vendor DSL solutions with the

capability to interoperate with products that conform to ANSI

and ETSI DSL standards.

GlobespanVirata’s unique hardware platform supports

multiple dual-channel applications including SDSL, HDSL2,

and SHDSL, using population options for optimization.

The XDSL2 DSL chip sets incorporate two DSL bit pumps

plus framing into a three-chip solution comprised of a dual-

channel digital signal processor (DSP) with built-in framer and

two Analog Front Ends each with an Integrated Line Driver

(ILD2).

The XDSL2 chip sets interface directly with off-the-shelf T1/

E1 transceivers and Nx64 multiplexing, eliminating the need

for a separate DSL framer to combine and format the two DSL

channels into a standard interface. GlobespanVirata’s DSL

XDSL2 chip sets deliver two channels of full duplex

transmission up to 2320 kb/s, depending on the application.

The high density XDSL2 dual-channel DSL chip sets are ideal

for CO applications, while single-channel versions with

integrated framer are also available for CPE applications.

Features

• Dual-channel DSP with framer that fully integrates

2 separate DSL chips into a single device

• Two AFEs, each with an integrated differential line driver

• 2B1Q, CAP, or PAM line codes

• Supports dual-channel symmetric data rates of 144 kb/s

to 2320 kb/s (depending on the application)

• Supports IDSL with optional data interface rates of

64 kb/s, 128 kb/s, and 144 kb/s

• Offers physical layer interoperability with competitive solu-

tions

• Glueless interface to popular microprocessors

• Transmission compliant with ETSI TS 101 135, ITU-T

G.991.1, and ANSI TR-28 for single pair 2B1Q and CAP,

ANSI T1.418 for HDSL2 and ITU-T G.991.2 for SHDSL

• Reference design compatible with Bellcore GR-1089, IEC

60950, UL 1950, ITU-T K.20 and K.21

• Built-in framer provides easy access to EOC and indicator

bits (framing can be bypassed completely for 2-channel

independent operation)

• Interfaces directly with off-the-shelf single-channel T1/E1

transceivers

• ATM UTOPIA Level 1 and 2 interface

• A single oscillator and hybrid topology supports all speeds

• +3.3V and +5V power supplies

Customer Interface

TDATA (A/B)

TClock (A/B)

Frame Pulse (A/B)

RDATA (A/B)

Rclock (A/B)

Frame Pulse (A/B)

Dual

Channel

DSP

w/Framer

µ Processor Interface

ILD2

ILD2

Figure 1. Block Diagram of XDSL2™ DSP with Two Single-Channel ILD2s

GlobespanVirata, Inc. — Proprietary

Use pursuant to Company Instructions

DO-009643-DS, Issue 2

1 page

June 25, 2002

XDSL2TM SDSL, HDSL2, and SHDSL - ILD2 Data Sheet

Table 1 describes the example arguments to the

SetParamXCVR() routine when performing start-up.

This is only a sample subset of possible parameters,

provided to illustrate how easy it is to work with the

GlobespanVirata chip sets.

Table 1. Example SetParamXCVR() Structure

Parameter

Function

GTI_ACTION_ITEM

GTI_MODE_ITEM

GTI_POWER_SCALE_ITEM

GTI_FRAMER_TYPE_ITEM

The action GTI_STARTUP_REQ begins

start-up, which, upon successful

completion, results in the transceiver

changing into DATA mode.

Mode describes which transceiver the

Host is talking to, the CO or CP.

Allows the transmit power to be set in

small increments.

The framing modes are interface specific.

Possible arguments for framing modes,

depending on the customer interface,

include: No Framing, UTOPIA Level 1,

UTOPIA Level 2, T1, E1, and nxDS0

(with the ability to choose continuous

DS0 blocks).

Checking the Transceiver Status

[SStatusXCVR()]

The SStatusXCVR() routine can be executed when in

DATA mode, utilizing minimal processing power. To

further illustrate the ease of programming

GlobespanVirata chip sets, Table 2 supplies a few

examples of SStatusXCVR().

Table 2. Example SStatusXCVR() Parameters

Parameter

Function

GTI_XMIT_POWER

GTI_START_PROGRESS

GTI_BERT_ERROR

GTI_RECEIVER_GAIN

This action returns the transmitted power.

The current detailed start-up state of the

transceiver is returned.

The number of bit errors detected during

the 511 BERT test is returned.

Total receiver gain setting can be calcu-

lated using the return values from this

action.

DO-009643-DS, Issue 2

GlobespanVirata, Inc. — Proprietary

Use pursuant to Company Instructions

5

5 Page

June 25, 2002

XDSL2TM SDSL, HDSL2, and SHDSL - ILD2 Data Sheet

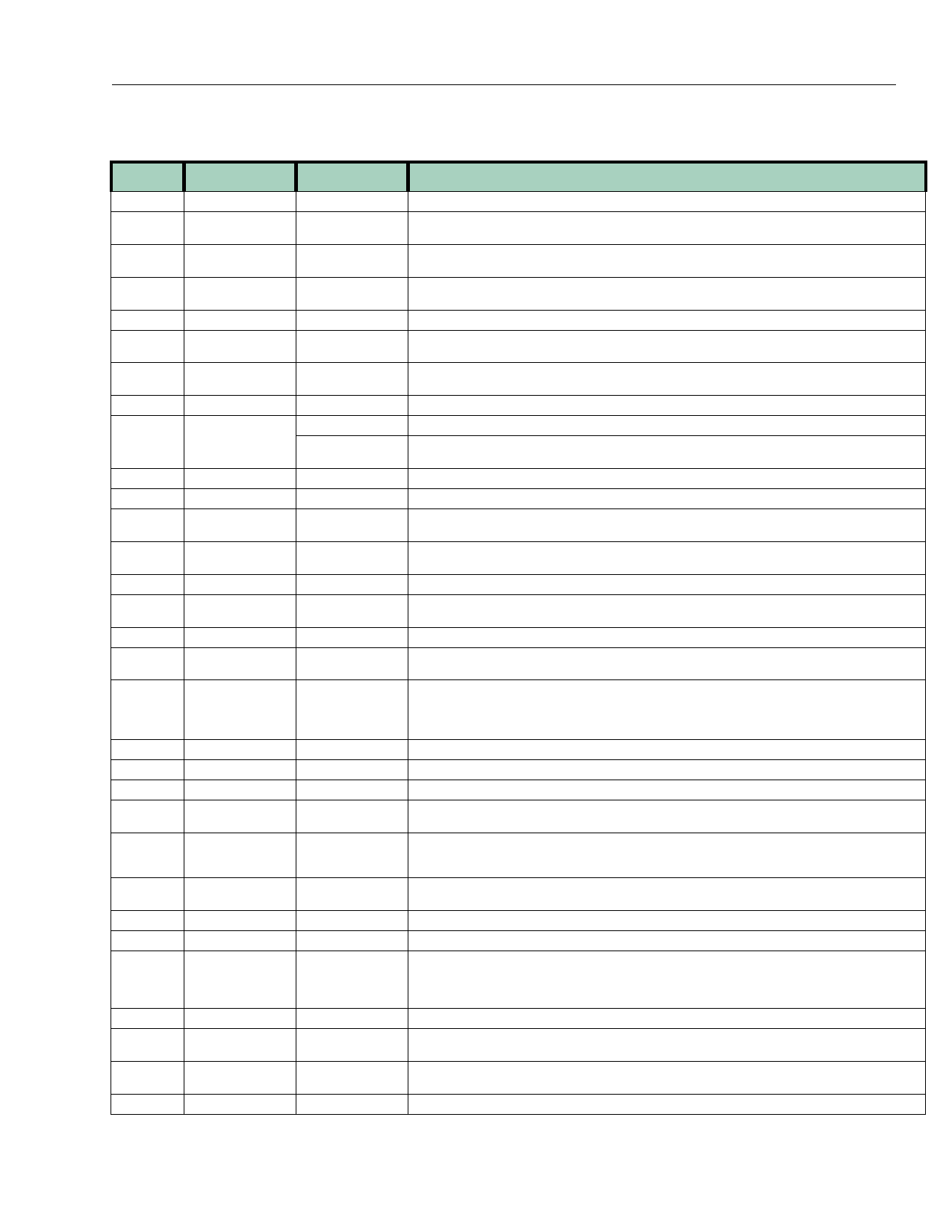

Table 12. 144-Pin Dual-Channel DSP/Framer Signal Descriptions

Pin Name(s)

Mode(s)

Functional Description

1 D2ACKA

2 APDO0

3 APDO1

4 APDO2

5 APDO3

6 APDO4

7 APDO5

8 VSS

9 CSCKA

10 CSDOA

11 A2DCKA

12 APDI0

13 APDI1

14 APDI2

15 APDI3

16 APDI4

17 APDI5

18 CSRD

19 VSS

20 VDD

21 BPDI0/APDI6

22 BPDI1/APDI7

23 BPDI2/APDI8

24 BPDI3/APDI9

25 BPDI4/APDI10

26 BPDI5/APDI11

27 A2DCKB

28 CSDOB

29 CSCKB

30 VSS

31 BPDO5/APDO11

32 BPDO4/APDO10

33 BPDO3/APDO9

I/O Not used for this application. Per application schematic, do not connect.

O

Data Out, Channel A. Data transmitted to ILD2 from DSP/Framer. Connected to ILD2 pin DACA for

channel A.

O

Control Output, Channel A. Control signal transmitted to ILD2 from DSP/Framer. Connected to ILD2 pin

CSD for channel A.

O

Master Clock to ILD2, Channel A. Input to AFE PLL which generates oversampling clocks. Connected

to ILD2 pin MCLK for channel A.

O Not used for this application. Per application schematic, do not connect.

I

Data In, Channel A. Data transmitted to DSP/Framer from ILD2. Connected to ILD2 pin Q0A for channel

A.

O

Data Out, Channel A. Data transmitted to ILD2 from DSP/Framer. Connected to ILD2 pin DACB for

channel A.

— Ground.

O Not used for Revision “B2” DSP/Framer applications. Per application schematic, do not connect.

I

TMS. Boundary-scan mode select. Applicable to Revision “C1” DSP/Framer applications only, for JTAG

support.

O Not used for this application. Per application schematic, do not connect.

I/O Not used for this application. Per application schematic, do not connect.

I

Data In, Channel A. Data transmitted to DSP/Framer from ILD2. Connected to ILD2 pin Q1A for channel

A.

I

Data In, Channel B. Data transmitted to DSP/Framer from ILD2. Connected to ILD2 pin Q1A for channel

B.

I Not used for this application. Per application schematic, pulled low through a 1kΩ resistor to ground.

I

Data In, Channel A. Data transmitted to DSP/Framer from ILD2. Connected to ILD2 pin Q1B for channel

A.

I Not used for this application. Per application schematic, pulled low through a 1kΩ resistor to ground.

I

Data In, Channel A. Data transmitted to DSP/Framer from ILD2. Connected to ILD2 pin Q0B for channel

A.

Not used for Revision “B2” DSP/Framer applications. Per application schematic, pulled low through

I a 1kΩ resistor to ground.

TDI. Boundary-scan data in. Applicable to Revision “C1” DSP/Framer applications only, for JTAG support.

— Ground.

P +3.3V supply.

I Not used for this application. Per application schematic, pulled low through a 1kΩ resistor to ground.

I

Data In, Channel B. Data transmitted to DSP/Framer from ILD2. Connected to ILD2 pin Q0B for channel

B.

I Not used for this application. Per application schematic, pulled low through a 1kΩ resistor to ground.

I

Data In, Channel B. Data transmitted to DSP/Framer from ILD2. Connected to ILD2 pin Q1B for channel

B.

I/O Not used for this application. Per application schematic, do not connect.

O Not used for this application. Per application schematic, do not connect.

Not used for Revision “B2” DSP/Framer applications. Per application schematic, do not connect.

O TDO. Boundary-scan data out. Applicable to Revision “C1” DSP/Framer applications only, for JTAG

support.

— Ground.

O

Data Out, Channel B. Data transmitted to ILD2 from DSP/Framer. Connected to ILD2 pin DACB for

channel B.

I

Data In, Channel B. Data transmitted to DSP/Framer from ILD2. Connected to ILD2 pin Q0A for channel

B.

O Not used for this application. Per application schematic, do not connect.

DO-009643-DS, Issue 2

GlobespanVirata, Inc. — Proprietary

Use pursuant to Company Instructions

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet G2214-208-041DFB2.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| G2214-208-041DFB2 | Transceiver | GlobespanVirata |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |