|

|

PDF MX25U8033E Data sheet ( Hoja de datos )

| Número de pieza | MX25U8033E | |

| Descripción | FLASH MEMORY | |

| Fabricantes | MACRONIX | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de MX25U8033E (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

MX25U8033E

MX25U8033E DATASHEET

P/N: PM1718

REV. 1.4, NOV. 06, 2013

1

http://www.Datasheet4U.com

1 page

MX25U8033E

8M-BIT [x 1/x 2/x 4] 1.8V CMOS MXSMIO (SERIAL MULTI I/O) FLASH MEMORY

FEATURES

GENERAL

• Single Power Supply Operation

- 1.65 to 2.0 volt for read, erase, and program operations

• Serial Peripheral Interface compatible -- Mode 0 and Mode 3

• 8M: 8,388,608 x 1 bit structure or 4,194,304 x 2 bits (two I/O read mode) structure or 2,097,152 x 4 bits (four I/O

read mode) structure

• 256 Equal Sectors with 4K byte each

- Any Sector can be erased individually

• 32 Equal Blocks with 32K byte each

- Any Block can be erased individually

• 16 Equal Blocks with 64K byte each

- Any Block can be erased individually

• Program Capability

- Byte base

- Page base (256 bytes)

• Latch-up protected to 100mA from -1V to Vcc +1V

PERFORMANCE

• High Performance

- Fast read

- 1 I/O: 80MHz with 8 dummy cycles

- 2 I/O: 80MHz with 4 dummy cycles, equivalent to 160MHz

- 4 I/O: 70MHz with 6 dummy cycles, equivalent to 280MHz;

- Fast program time: 1.2ms(typ.) and 3.0ms(max.)/page (256-byte per page)

- Byte program time: 10us (typ.)

- Fast erase time

- 30ms(typ.) and 200ms(max.)/sector (4K-byte per sector)

- 200ms(typ.) and 1000ms(max.)/block (32K-byte per block)

- 500ms(typ.) and 2000ms(max.)/block (64K-byte per block)

- 5.0s(typ.) and 10s(max.)/chip

• Low Power Consumption

- Low active read current: 12mA(max.) at 80MHz, 7mA(max.) at 33MHz

- Low active erase/programming current: 25mA (max.)

- Low standby current: 8uA (typ.)/30uA (max.)

• Low Deep Power Down current: 8uA(max.)

• Typical 100,000 erase/program cycles

• 20 years data retention

SOFTWARE FEATURES

• Input Data Format

- 1-byte Command code

• Advanced Security Features

- Block lock protection

The BP0-BP3 status bit defines the size of the area to be software protection against program and erase instruc-

tions

- Additional 4K-bit secured OTP for unique identifier

• Auto Erase and Auto Program Algorithm

- Automatically erases and verifies data at selected sector or block

- Automatically programs and verifies data at selected page by an internal algorithm that automatically times the

program pulse widths (Any page to be programed should have page in the erased state first).

P/N: PM1718

REV. 1.4, NOV. 06, 2013

5

http://www.Datasheet4U.com

5 Page

MX25U8033E

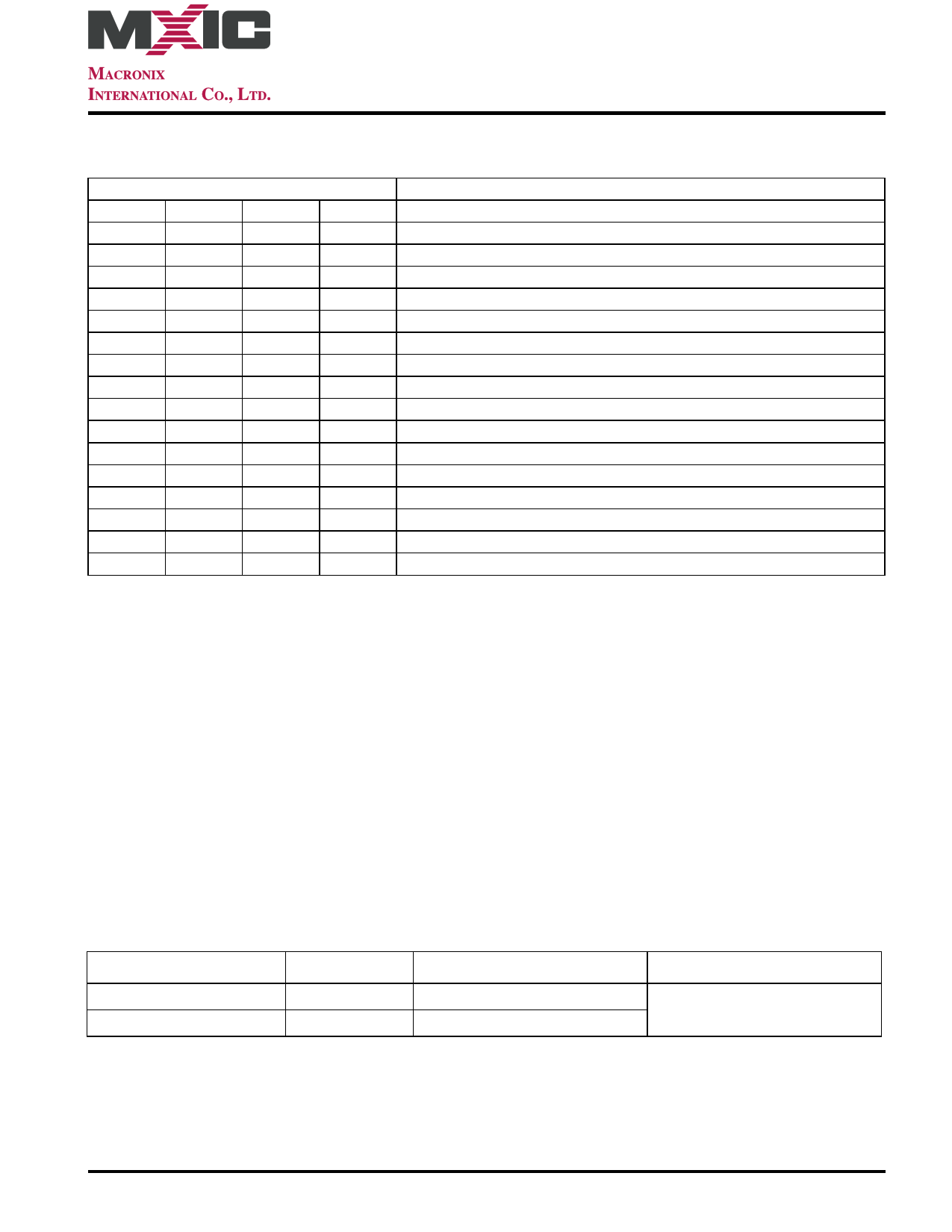

Table 2. Protected Area Sizes

Status Bit

BP3 BP2 BP1

000

000

001

001

010

010

011

011

100

100

101

101

110

110

111

111

Protect Level

BP0 8Mb

0 0 (none)

1 1 (1block, protected block 15th)

0 2 (2blocks, protected block 14th~15th)

1 3 (4blocks, protected block 12nd~15th)

0 4 (8blocks, protected block 8th~15th)

1 5 (16blocks, protected all)

0 6 (16blocks, protected all)

1 7 (16blocks, protected all)

0 8 (16blocks, protected all)

1 9 (16blocks, protected all)

0 10 (16blocks, protected all)

1 11 (8blocks, protected block 0th~7th)

0 12 (12blocks, protected block 0th~11st)

1 13 (14blocks, protected block 0th~13rd)

0 14 (15blocks, protected block 0th~14th)

1 15 (16blocks, protected all)

II. Additional 4K-bit secured OTP for unique identifier: to provide 4K-bit One-Time Program area for setting de-

vice unique serial number - Which may be set by factory or system maker. Please refer to Table 3. 4K-bit Se-

cured OTP Definition.

- Security register bit 0 indicates whether the chip is locked by factory or not.

- To program the 4K-bit secured OTP by entering 4K-bit secured OTP mode (with ENSO command), and going

through normal program procedure, and then exiting 4K-bit secured OTP mode by writing EXSO command.

- Customer may lock-down the customer lockable secured OTP by writing WRSCUR(write security register)

command to set customer lock-down bit1 as "1". Please refer to table of "Security Register Definition" for security

register bit definition and table of "4K-bit Secured OTP Definition" for address range definition.

Note:

Once lock-down whatever by factory or customer, it cannot be changed any more. While in 4K-bit Secured OTP

mode, array access is not allowed.

Table 3. 4K-bit Secured OTP Definition

Address range

xxx000~xxx00F

xxx010~xxx1FF

Size

128-bit

3968-bit

Standard Factory Lock

ESN (electrical serial number)

N/A

Customer Lock

Determined by customer

P/N: PM1718

11

REV. 1.4, NOV. 06, 2013

http://www.Datasheet4U.com

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet MX25U8033E.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MX25U8033E | FLASH MEMORY | MACRONIX |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |