|

|

PDF 74LVC595A Data sheet ( Hoja de datos )

| Número de pieza | 74LVC595A | |

| Descripción | 8-bit serial-in/serial-out or parallel-out shift register | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de 74LVC595A (archivo pdf) en la parte inferior de esta página. Total 19 Páginas | ||

|

No Preview Available !

74LVC595A

www.DataSheet4U.com

8-bit serial-in/serial-out or parallel-out shift register; 3-state

Rev. 01 — 29 May 2007

Product data sheet

1. General description

The 74LVC595A is an 8-bit serial-in/serial or parallel-out shift register with a storage

register and 3-state outputs. Both the shift and storage register have separate clocks.

The input can be driven from either 3.3 V or 5 V devices. This feature allows the use of

this device in a mixed 3.3 V and 5 V environment.

This device is fully specified for partial Power-down applications using IOFF.

The IOFF circuitry disables the output, preventing the damaging backflow current through

the device when it is powered down.

Data is shifted on the positive-going transitions of the SHCP input. The data in the shift

register is transferred to the storage register on a positive-going transition of the STCP

input. If both clocks are connected together, the shift register will always be one clock

pulse ahead of the storage register.

The shift register has a serial input (DS) and a serial output (Q7S) for cascading

purposes. It is also provided with asynchronous reset input MR (active LOW) for all 8 shift

register stages. The storage register has 8 parallel 3-state bus driver outputs. Data in the

storage register appears at the output whenever the output enable input (OE) is LOW.

2. Features

s 5 V tolerant inputs/outputs for interfacing with 5 V logic

s Wide supply voltage range from 1.2 V to 3.6 V

s CMOS low-power consumption

s Direct interface with TTL levels

s Balanced propagation delays

s All inputs have Schmitt-trigger action

s Complies with JEDEC standard JESD8-B/JESD36

s ESD protection:

x HBM JESD22-A114-D exceeds 2000 V

x CDM JESD22-C101-C exceeds 1000 V

s Specified from −40 °C to +85 °C and −40 °C to +125 °C.

3. Applications

s Serial-to-parallel data conversion

s Remote control holding register

1 page

NXP Semiconductors

74LVC595A

www.DataSheet4U.com

8-bit serial-in/serial-out or parallel-out shift register; 3-state

7. Functional description

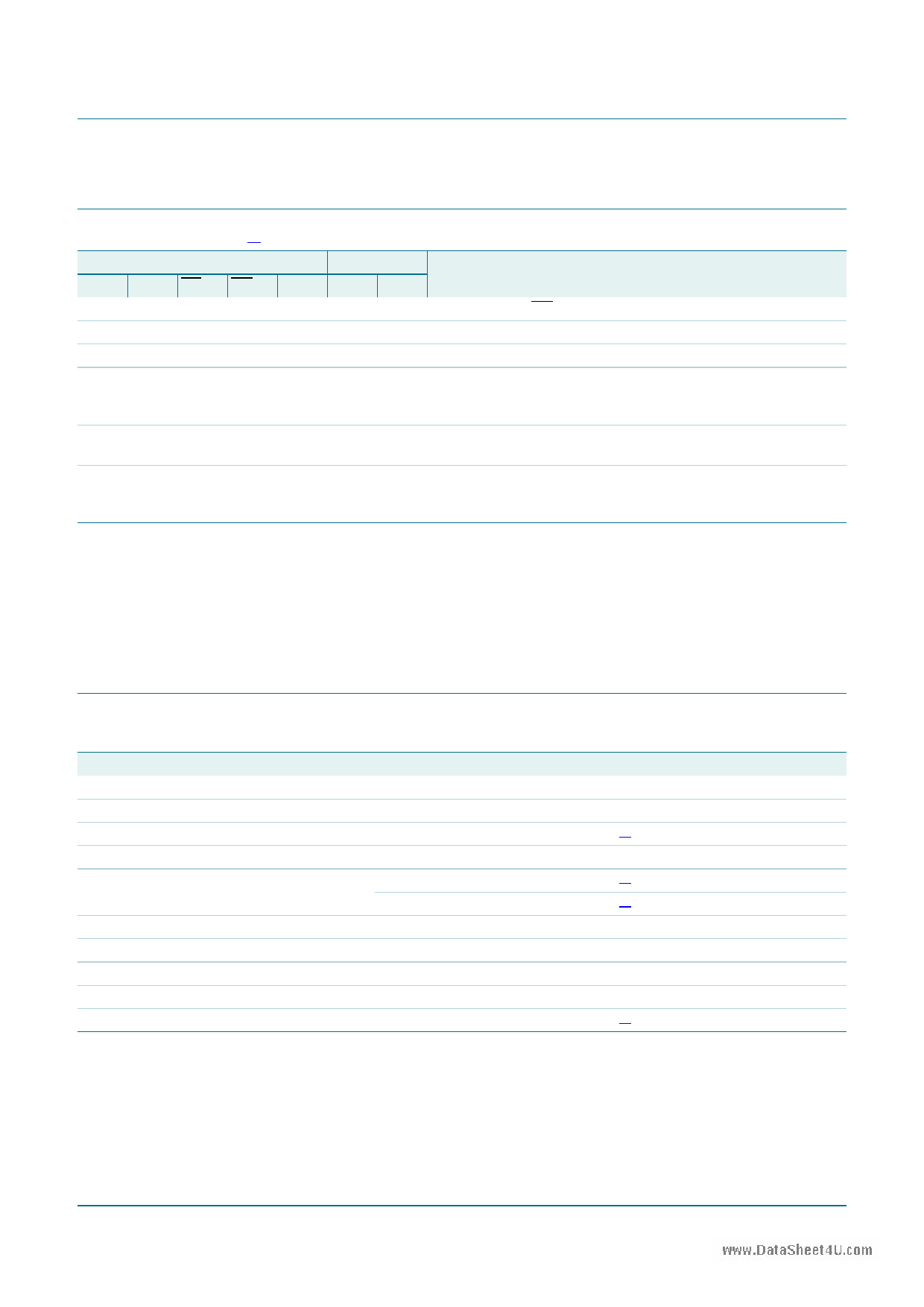

Table 3. Function table[1]

Input

SHCP STCP OE MR

XXL L

X↑L L

XXHL

↑XL H

DS

X

X

X

H

X↑ L HX

↑ ↑ L HX

[1] H = HIGH voltage state;

L = LOW voltage state;

↑ = LOW-to-HIGH transition;

X = don’t care;

NC = no change;

Z = high-impedance OFF-state.

Output

Q7S Qn

L NC

LL

LZ

Q6S NC

NC QnS

Q6S QnS

Function

a LOW-state on MR only affects the shift register

empty shift register loaded into storage register

shift register clear; parallel outputs in high impedance OFF-state

logic HIGH-state shifted into shift register stage 0. Contents of all

shift register stages shifted through, e.g. previous state of stage 6

(internal Q6S) appears on the serial output (Q7S).

contents of shift register stages (internal QnS) are transferred to

the storage register and parallel output stages

contents of shift register shifted through; previous contents of the

shift register is transferred to the storage register and the parallel

output stages

8. Limiting values

Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).

Symbol

Parameter

Conditions

Min Max

Unit

VCC

IIK

VI

IOK

VO

IO

ICC

IGND

Tstg

Ptot

supply voltage

input clamping current

input voltage

output clamping current

output voltage

output current

supply current

ground current

storage temperature

total power dissipation

VI < 0 V

VO > VCC or VO < 0 V

3-state

output HIGH or LOW state

VO = 0 V to VCC

Tamb = −40 °C to +125 °C

−0.5

−50

[1] −0.5

-

[1] −0.5

[1] −0.5

-

-

−100

−65

[2] -

+6.5

-

+6.5

±50

6.5

VCC + 0.5

±50

100

-

+150

500

V

mA

V

mA

V

V

mA

mA

mA

°C

mW

[1] The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

[2] For SO16 packages: above 70 °C the value of Ptot derates linearly with 8 mW/K.

For TSSOP16 packages: above 60 °C the value of Ptot derates linearly with 5.5 mW/K.

For DHVQFN16 packages: above 60 °C the value of Ptot derates linearly with 4.5 mW/K.

74LVC595A_1

Product data sheet

Rev. 01 — 29 May 2007

© NXP B.V. 2007. All rights reserved.

5 of 19

5 Page

NXP Semiconductors

74LVC595A

www.DataSheet4U.com

8-bit serial-in/serial-out or parallel-out shift register; 3-state

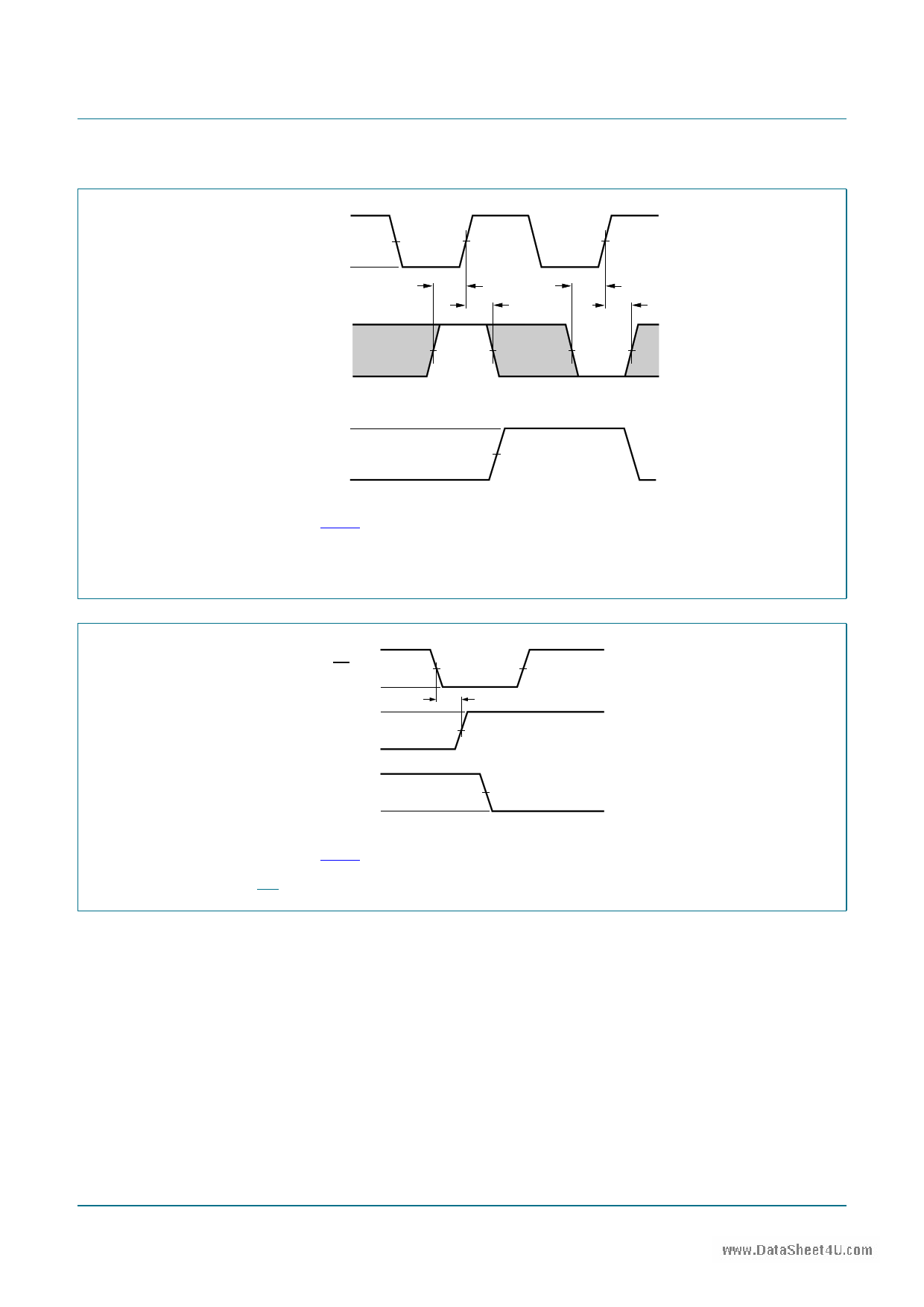

VI

SHCP input

GND

VI

DS input

GND

VM

t su

th

VM

t su

th

VOH

Q7S output

VOL

VM

mna560

Measurement points are given in Table 8.

The shaded areas indicate when the input is permitted to change for predictable output performance.

VOL and VOH are typical output voltage drops that occur with the output load.

Fig 9. The data set-up and hold times for the serial data input (DS)

VI

MR input

GND

VI

STCP input

GND

VOH

Qn outputs

VOL

VM

tsu

VM

VM

001aaf571

Measurement points are given in Table 8.

VOL and VOH are typical output voltage drops that occur with the output load.

Fig 10. The master reset (MR) to storage clock (STCP) set-up times

74LVC595A_1

Product data sheet

Rev. 01 — 29 May 2007

© NXP B.V. 2007. All rights reserved.

11 of 19

11 Page | ||

| Páginas | Total 19 Páginas | |

| PDF Descargar | [ Datasheet 74LVC595A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 74LVC595A | 8-bit serial-in/serial-out or parallel-out shift register | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |