|

|

PDF GS78116B Data sheet ( Hoja de datos )

| Número de pieza | GS78116B | |

| Descripción | 512K x 16 8Mb Asynchronous SRAM | |

| Fabricantes | GSI Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de GS78116B (archivo pdf) en la parte inferior de esta página. Total 11 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

BGA

Commercial Temp

Industrial Temp

512K x 16

8Mb Asynchronous SRAM

Features

• Fast access time: 10, 12, 15 ns

• CMOS low power operation: 300/250/220/180 mA at

minimum cycle time

• Single 3.3 V ± 0.3 V power supply

• All inputs and outputs are TTL-compatible

• Fully static operation

• Industrial Temperature Option: –40° to 85°C

• 14 mm x 22 mm, 119-Bump, 1.27 mm Pitch Ball Grid Array

package

Description

The GS78116 is a high speed CMOS static RAM organized as

524,288-words by 16-bits. Static design eliminates the need for

external clocks or timing strobes. The GS78116 operates on a

single 3.3 V power supply and all inputs and outputs are TTL-

compatible. The GS78116 is available in 14 mm x 22 mm

BGA package.

Pin Descriptions

Symbol

A0 to A18

DQ1 to DQ16

CE

WE

OE

VDD

VSS

NC

GS78116B

10, 12, 15 ns

3.3 V VDD

Description

Address input

Data input/output

Chip enable input

Write enable input

Output enable input

+3.3 V power supply

Ground

No connect

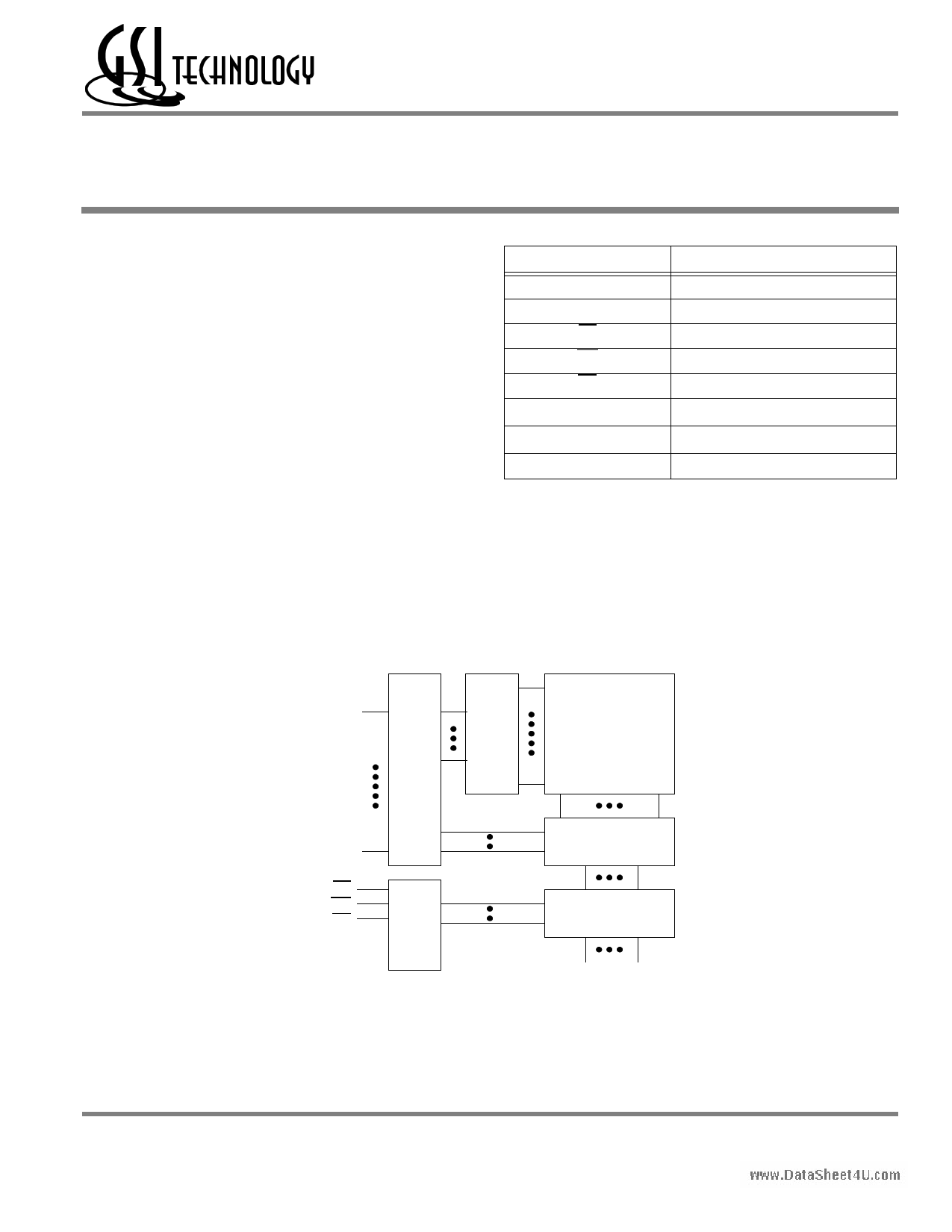

Block Diagram

A0 Row

Decoder

Address

Input

Buffer

A18

CE

WE

OE

Control

Memory Array

Column

Decoder

I/O Buffer

DQ1 DQ16

Rev: 1.02 9/2001

For latest documentation see http://www.gsitechnology.com.

1/11

© 1999, Giga Semiconductor, Inc.

1 page

www.DataSheet4U.com

AC Test Conditions

Parameter

Conditions

Input high level

Input low level

Input rise time

VIH = 2.4 V

VIL = 0.4 V

tr = 1 V/ns

Input fall time

tf = 1 V/ns

Input reference level

1.4 V

Output reference level

1.4 V

Output load

Fig. 1& 2

Notes:

1. Include scope and jig capacitance.

2. Test conditions as specified with output loading as shown in Fig. 1

unless otherwise noted

3. Output load 2 for tLZ, tHZ, tOLZ and tOHZ.

GS78116B

Output Load 1

DQ

50Ω 30pF1

VT = 1.4 V

Output Load 2

3.3 V

DQ 589Ω

5pF1 434Ω

AC Characteristics

Read Cycle

Parameter

Read cycle time

Address access time

Chip enable access time (CE)

Output enable to output valid (OE)

Output hold from address change

Chip enable to output in low Z (CE)

Output enable to output in low Z (OE)

Chip disable to output in High Z (CE)

Output disable to output in High Z (OE)

Symbol

tRC

tAA

tAC

tOE

tOH

tLZ*

tOLZ*

tHZ*

tOHZ*

-10

Min Max

10 —

— 10

— 10

—4

3—

3—

0—

—5

—4

-12

Min Max

12 —

— 12

— 12

—5

3—

3—

0—

—6

—5

-15

Min Max

15 —

— 15

— 15

—6

3—

3—

0—

—7

—6

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

Rev: 1.02 9/2001

For latest documentation see http://www.gsitechnology.com.

5/11

© 1999, Giga Semiconductor, Inc.

5 Page

www.DataSheet4U.com

GS78116B

Asynchronous SRAM Datasheet Revision History

Rev. Code: Old;

New

GS78116Rev0.01a 5/1999;

1.00 X/1999

GS78116Rev 1.0010/1999A;Rev

1.01 2/2000FormatB

Rev 1.01 2/2000FormatB;

78116_r1_02

Types of Changes

Format or Content

Page #/Revisions/Reason

Format/Typos

• p.2/Changed E to CE/consistency.

Content

• p.2/Changed Pin T1 from BA to BD/Correction

• Added GSI Logo

Format/Content

• Updated format to comply with Technical Publication standards

• Finalized document and removed preliminary references

Rev: 1.02 9/2001

For latest documentation see http://www.gsitechnology.com.

11/11

© 1999, Giga Semiconductor, Inc.

11 Page | ||

| Páginas | Total 11 Páginas | |

| PDF Descargar | [ Datasheet GS78116B.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| GS78116AB | 512K x 16 8Mb Asynchronous SRAM | GSI Technology |

| GS78116B | 512K x 16 8Mb Asynchronous SRAM | GSI Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |