|

|

PDF GS1500 Data sheet ( Hoja de datos )

| Número de pieza | GS1500 | |

| Descripción | HDTV Serial Digital Deformatter | |

| Fabricantes | Gennum Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de GS1500 (archivo pdf) en la parte inferior de esta página. Total 17 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

FEATURES

• SMPTE 292M compliant

• standards detection/indication for SMPTE 292M levels

A/B,C,D/E,F,G/H,I,J/K,L/M

• NRZI decoding and SMPTE descrambling with

BYPASS option

• line CRC calculation, comparison

• selectable line based CRC re-insertion

• H, V, F timing reference signal (TRS) extraction

• selectable flywheel for noise immune H, V, F extraction

• selectable automatic switch line handling

• selectable TRS and line number re-insertion

• selectable active picture illegal code re-mapping

• ANC data position indication

• ANC data extraction via internal FIFOs

(1024 bytes on Y and C channels)

• configurable FIFO LOAD pulse

• 20 bit 3.3V CMOS input data bus

• optimized input interface to GS1545 or GS1540

• single +3.3V power supply

• 5V tolerant I/O

APPLICATIONS

SMPTE 292M Serial Digital Interfaces.

HD-LINX ™ GS1500

HDTV Serial Digital Deformatter

with ANC FIFOs

PRELIMINARY DATA SHEET

DESCRIPTION

When interfaced to the Gennum GS1545 HDTV Equalizing

Receiver or GS1540 Non-Equalizing Receiver, the GS1500

performs the final conversion to word aligned data. The

device performs NRZI decoding and de-scrambling as per

SMPTE 292M and word-aligns to the incoming data stream.

Line based CRCs are calculated on the incoming data

stream and are compared against the CRCs embedded

within the data stream.

HVF timing information is extracted from the data stream. A

selectable internal HVF flywheel provides superior noise

immunity against TRS signal errors. The device also detects

and indicates the input video signal standard.

The GS1500 can detect and re-map illegal code words

contained within the active portion of the video signal. The

positions of the embedded ANC data are indicated and the

ANC data may be extracted and accessed by the user

through an internal FIFO interface. Prior to exiting the

device, TRS, Line Numbers and CRCs based on internal

calculations may be re-inserted into the data stream.

ORDERING INFORMATION

PART NUMBER

PACKAGE

GS1500-CQR

128 pin MQFP

TEMPERATURE

0°C to 70°C

DATA_IN

[19:0]

INPUT

BUFFER

PCLK_IN

WB_NI

BP_DSC

BP_FR

3

FW_EN/DIS

FAST_LOCK

TRS_Y/C

F_E/S

2

RESET

2 MUTE

EX/CP

FM_I/E

R_CLK

CODE

PROTECT

2

ANC_Y/C ANC/DATA

DESCRAMBLE

FRAME

TRS DETECTION

FLYWHEEL

STANDARD

DETECTION

TRS

EXTRACTION

CRC

CALCULATION

CRC

COMPARISON

ILLEGAL CODE REMAPPING

ANC DATA DETECTION &

EXTRACTION FIFO'S

TRS_INS

LN_INS

CRC_INS

3

TRS,

LNUM,

AND CRC

INSERTION

DATA_OUT

[19:10]

(LUMA)

DATA_OUT

[9:0]

(CHROMA)

3

[H:V:F]

3 FIFO_L

4

10

ANC_OUT

[9:0]

2

2 FFRST

FOEN

3

FF_STA

2 [2:0]

2

LN_ERR

SAV_ERR

EAV_ERR

VD_STD

[3:0]

2

LINE_CRC_ERR[Y:C]

ANC_DATA

[Y:C]

REN

WEN

YCS_ERR

CCS_ERR

OEN

BLOCK DIAGRAM

Revision Date: November 2000

Document No. 522 - 33 - 00

GENNUM CORPORATION P.O. Box 489, Stn. A, Burlington, Ontario, Canada L7R 3Y3

Tel. +1 (905) 632-2996 Fax. +1 (905) 632-5946 E-mail: [email protected]

www.gennum.com

1 page

PIN DESCRIPTIONS (Continued)

NUMBER

SYMBOL

TIMING

13

TRS_INS

Non-

synchronous

15

LN_INS

Non-

synchronous

16

CRC_INS

Non-

synchronous

17

FAST_LOCK

Synchronous

wrt PCLK_IN

18

RESET

Non-

synchronous

21 H Synchronous

wrt PCLK_IN

22 V Synchronous

wrt PCLK_IN

23 F Synchronous

wrt PCLK_IN

26

ANC_DATA_Y

Synchronous

wrt PCLK_IN

TYPE

DESCRIPTION

Input

Control Signal Input. Used to enable or disable re-insertion of the

TRS into the data stream. When TRS_INS is high, the device re-

inserts TRS into the incoming data stream based on the internal

calculation. The original TRS packets are set to the blanking levels.

If the flywheel is enabled, TRS calculated by the flywheel is used for

insertion. When TRS_INS is low, the device will not re-insert TRS

even if errors in TRS signals are detected.

Input

Control Signal Input. Used to enable or disable re-insertion of the

line number into the data stream. When LN_INS is high, the device

re-inserts the line number into the incoming data stream based on

the internal calculation. The original line number packets are set to

the blanking levels. If the flywheel is enabled, the line number

calculated by the flywheel is used for insertion. When LN_INS is low,

the device will not re-insert the line number.

Input

Control Signal Input. Used to enable or disable re-insertion of the

CRC into the data stream. When CRC_INS is high, the device is

enabled to re-insert line CRCs based on the internal calculation.

When CRC_INS is low, the device will not re-insert the CRCs.

Input

Control Signal Input. Used to control the flywheel synchronization

when a switch line occurs. When a low to high transition occurs on

the FAST_LOCK signal, the internal flywheel will immediately re-

synchronize to the next valid EAV or SAV TRS in the incoming data

stream. See Fig. 5 for timing information.

Input

Control Signal Input. Used to reset the system state registers to their

default 720p parameters. When RESET is high, the fly wheel, TRS

Detection, and ANC Detection operate normally. When RESET is

low, the flywheel, TRS Detection, and ANC Detection are reset to the

720p parameters after a rising edge on PCLK_IN. The read and

write counters are not affected.

Output

Control Signal Output. This signal indicates the Horizontal blanking

period of the video signal. Refer to Fig. 2 for timing information of H

relative to DATA_OUT[19:10] and DATA_OUT[9:0], LUMA and

CHROMA respectively.

Output

Control Signal Output. This signal indicates the Vertical blanking

period of the video signal. Refer to Fig. 2 for timing information of V

relative to DATA_OUT[19:10] and DATA_OUT[9:0], LUMA and

CHROMA respectively.

Output

Control Signal Output. This signal indicates the ODD/EVEN field of

the video signal. Refer to Fig. 2 for timing information of F relative to

DATA_OUT[19:10] and DATA_OUT[9:0], LUMA and CHROMA

respectively. When locked and the input signal is of a progressive

scan nature, F stays low at all times.

Output

Control Signal Output. This signal indicates the position of the

embedded ANC data in the outgoing LUMA (DATA_OUT [19:10])

data stream. ANC_DATA_Y goes high for the entire time that an

ANC_DATA packet is present in the LUMA (DATA_OUT[19:10]) data

stream whether it be in the active video area or the ANC area. Refer

to Fig. 17 for timing of ANC_DATA_Y relative to LUMA

(DATA_OUT[19:10]). During detection of ANC data, any errors in the

data count (DC) packet will consequently cause errors in the

duration of the flags. Bit errors in an ANC header will prevent the

packet from being detected.

GENNUM CORPORATION

5

522 - 33 - 00

5 Page

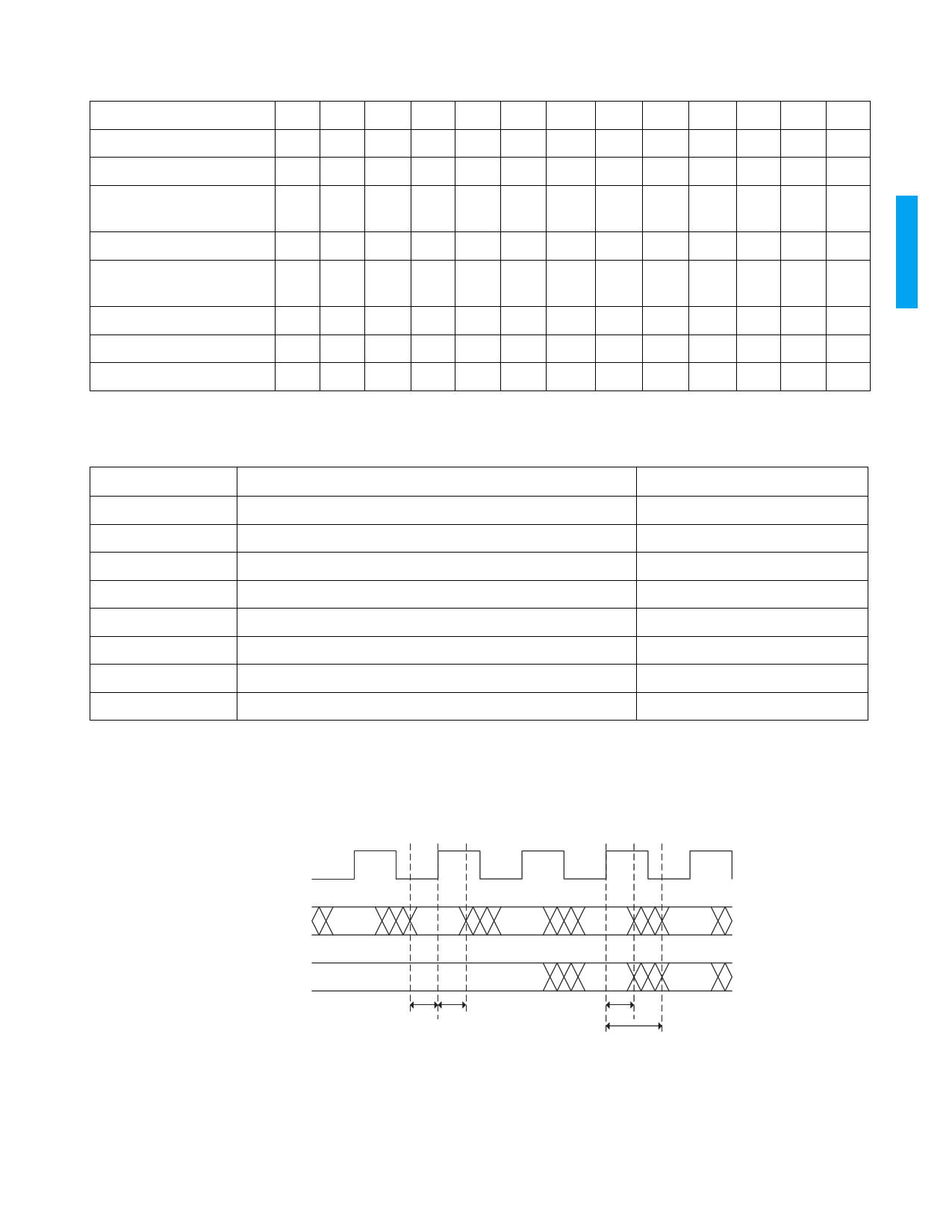

TABLE 3: Source Format Parameters

Reference SMPTE Standard 260m 260m 295m 274m 274m 274m 274m 274m 274m 274m 274m 296m 296m

Format ID

ABCDE F G H I J KLM

Lines/Frame

1125 1125 1250 1125 1125 1125 1125 1125 1125 1125 1125 750 750

Words/Active Line

(each channel Y, Cb/Cr)

1920 1920 1920 1920 1920 1920 1920 1920 1920 1920 1920 1280 1280

Total Active Lines

1035 1035 1080 1080 1080 1080 1080 1080 1080 1080 1080 720 720

Words/Total Line

(each channel Y, Cb/Cr)

2200 2200 2376 2200 2200 2640 2200 2200 2640 2750 2750 1650 1650

Frame Rate (Hz)

30 30/M 25

30 30/M 25

30 30/M 25

24 24/M 60 60/M

Fields /Frame

222222 1 1 1 1 111

Data Rate Divisor

1M1 1M1 1 M 1 1 M1M

NOTE: M=1.001 in the above table.

TABLE 4: FIFO Status Indicator

FF_STA[2:0]

DESCRIPTION

000 ERROR Flag; FIFO is under run

001 FIFO is empty

010 FIFO is almost empty; <= 32 bytes filled

011 FIFO is ready

100 FIFO is half full

101 FIFO is almost full; >= 992 bytes filled

110 FIFO is full

111 ERROR Flag; FIFO is over run

SYNCHRONIZED TO

R_CLK

R_CLK

R_CLK

-

PCLK_IN

PCLK_IN

PCLK_IN

PCLK_IN

PCLK_IN

DATA_IN

DATA_OUT

DATA

DATA

DATA

DATA

DATA

DATA

tSU tIH

Fig. 1 Synchronous I/O Timing

tOH

tOD

DATA

GENNUM CORPORATION

11

522 - 33 - 00

11 Page | ||

| Páginas | Total 17 Páginas | |

| PDF Descargar | [ Datasheet GS1500.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| GS1500 | HDTV Serial Digital Deformatter | Gennum Corporation |

| GS1501 | HDTV Serial Digital Formatter | Gennum Corporation |

| GS1503 | HD EMBEDDED AUDIO CODEC | Gennum Corporation |

| GS1504 | HDTV Adaptive Equalizer | ETC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |