|

|

PDF GS82032A Data sheet ( Hoja de datos )

| Número de pieza | GS82032A | |

| Descripción | 64K x 32 / 2M Synchronous Burst SRAM | |

| Fabricantes | GSI Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de GS82032A (archivo pdf) en la parte inferior de esta página. Total 23 Páginas | ||

|

No Preview Available !

GS82032AT/Q-180/166/133/100

TQFP, QFP

Commercial Temp

Industrial Temp

64K x 32

2M Synchronous Burst SRAM

180 MHz–100 MHz

8 ns–12 ns

3.3 V VDD

3.3 V and 2.5 V I/O

Features

• FT pin for user-configurable flow through or pipelined

operation

• Single Cycle Deselect (SCD) operation

• 3.3 V +10%/–5% core power supply

• 2.5 V or 3.3 V I/O supply

• LBO pin for Linear or Interleaved Burst mode

• Internal input resistors on mode pins allow floating mode pins

• Default to Interleaved Pipelined mode

• Byte Write (BW) and/or Global Write (GW) operation

• Common data inputs and data outputs

• Clock Control, registered, address, data, and control

• Internal self-timed write cycle

• Automatic power-down for portable applications

• JEDEC standard 100-lead TQFP or QFP package

Pipeline

3-1-1-1

Flow

Through

2-1-1-1

tCycle

tKQ

IDD

tCycle

tKQ

IDD

-180

5.5 ns

3.2 ns

155 mA

9.1 ns

8 ns

100 mA

-166

6 ns

3.5 ns

140 mA

10 ns

8.5 ns

90 mA

-133

7.5 ns

4 ns

115 mA

12 ns

10 ns

80 mA

-100

10 ns

5 ns

90 mA

15 ns

12 ns

65 mA

Functional Description

Applications

The GS82032A is a 2,097,152-bit high performance

synchronous SRAM with a 2-bit burst address counter.

Although of a type originally developed for Level 2 Cache

applications supporting high performance CPUs, the device

now finds application in synchronous SRAM applications,

ranging from DSP main store to networking chip set support.

Controls

Addresses, data I/Os, chip enables (E1, E2, E3), address burst

control inputs (ADSP, ADSC, ADV), and write control inputs

(Bx, BW, GW) are synchronous and are controlled by a

positive-edge-triggered clock input (CK). Output enable (G)

and power down control (ZZ) are asynchronous inputs. Burst

cycles can be initiated with either ADSP or ADSC inputs. In

Burst mode, subsequent burst addresses are generated

internally and are controlled by ADV. The burst address

counter may be configured to count in either linear or

interleave order with the Linear Burst Order (LBO) input. The

Burst function need not be used. New addresses can be loaded

on every cycle with no degradation of chip performance.

Flow Through/Pipeline Reads

The function of the Data Output Register can be controlled by

the user via the FT mode pin (Pin 14 in the TQFP). Holding

the FT mode pin low places the RAM in Flow Through mode,

causing output data to bypass the Data Output Register.

Holding FT high places the RAM in Pipelined mode, activating

the rising-edge-triggered Data Output Register.

SCD Pipelined Reads

The GS82032A is an SCD (Single Cycle Deselect) pipelined

synchronous SRAM. DCD (Dual Cycle Deselect) versions are

also available. SCD SRAMs pipeline deselect commands one

stage less than read commands. SCD RAMs begin turning off

their outputs immediately after the deselect command has been

captured in the input registers.

Byte Write and Global Write

Byte write operation is performed by using Byte Write enable

(BW) input combined with one or more individual byte write

signals (Bx). In addition, Global Write (GW) is available for

writing all bytes at one time, regardless of the Byte Write

control inputs.

Sleep Mode

Low power (Sleep mode) is attained through the assertion

(High) of the ZZ signal, or by stopping the clock (CK).

Memory data is retained during Sleep mode.

Core and Interface Voltages

The GS82032A operates on a 3.3 V power supply and all

inputs/outputs are 3.3 V- and 2.5 V-compatible. Separate

output power (VDDQ) pins are used to decouple output noise

from the internal circuit.

Rev: 1.09 7/2002

1/23

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

© 2000, Giga Semiconductor, Inc.

1 page

GS82032AT/Q-180/166/133/100

Mode Pin Functions

Mode Name

Pin Name State

Function

Burst Order Control

LBO

L

H or NC

Linear Burst

Interleaved Burst

Output Register Control

L

FT

H or NC

Flow Through

Pipeline

Power Down Control

L or NC

ZZ H

Active

Standby, IDD = ISB

Note:

There are pull-up devices on LBO and FT pins and a pull-down device on the ZZ pin, so those input pins can be

unconnected and the chip will operate in the default states as specified in the above table.

Burst Counter Sequences

Linear Burst Sequence

Interleaved Burst Sequence

A[1:0] A[1:0] A[1:0] A[1:0]

A[1:0] A[1:0] A[1:0] A[1:0]

1st address

00 01 10 11

1st address

00 01 10 11

2nd address

01 10 11 00

2nd address

01 00 11 10

3rd address

10 11 00 01

3rd address

10 11 00 01

4th address

11 00 01 10

Note: The burst counter wraps to initial state on the 5th clock.

4th address

11 10 01 00

Note: The burst counter wraps to initial state on the 5th clock.

Byte Write Truth Table

Function

GW BW

BA

BB

BC

BD Notes

Read H H X X X X 1

Read H L H H H H 1

Write byte A

H

L

L

H

H

H 2, 3

Write byte B

H

L

H

L

H

H 2, 3

Write byte C

H

L

H

H

L

H 2, 3, 4

Write byte D

H

L

H

H

H

L 2, 3, 4

Write all bytes

H

L

L

L

L

L 2, 3, 4

Write all bytes

L

X

X

X

X

X

Notes:

1. All byte outputs are active in read cycles regardless of the state of Byte Write Enable inputs.

2. Byte Write Enable inputs BA, BB, BC and/or BD may be used in any combination with BW to write single or multiple bytes.

3. All byte I/Os remain High-Z during all write operations regardless of the state of Byte Write Enable inputs.

Rev: 1.09 7/2002

5/23

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

© 2000, Giga Semiconductor, Inc.

5 Page

GS82032AT/Q-180/166/133/100

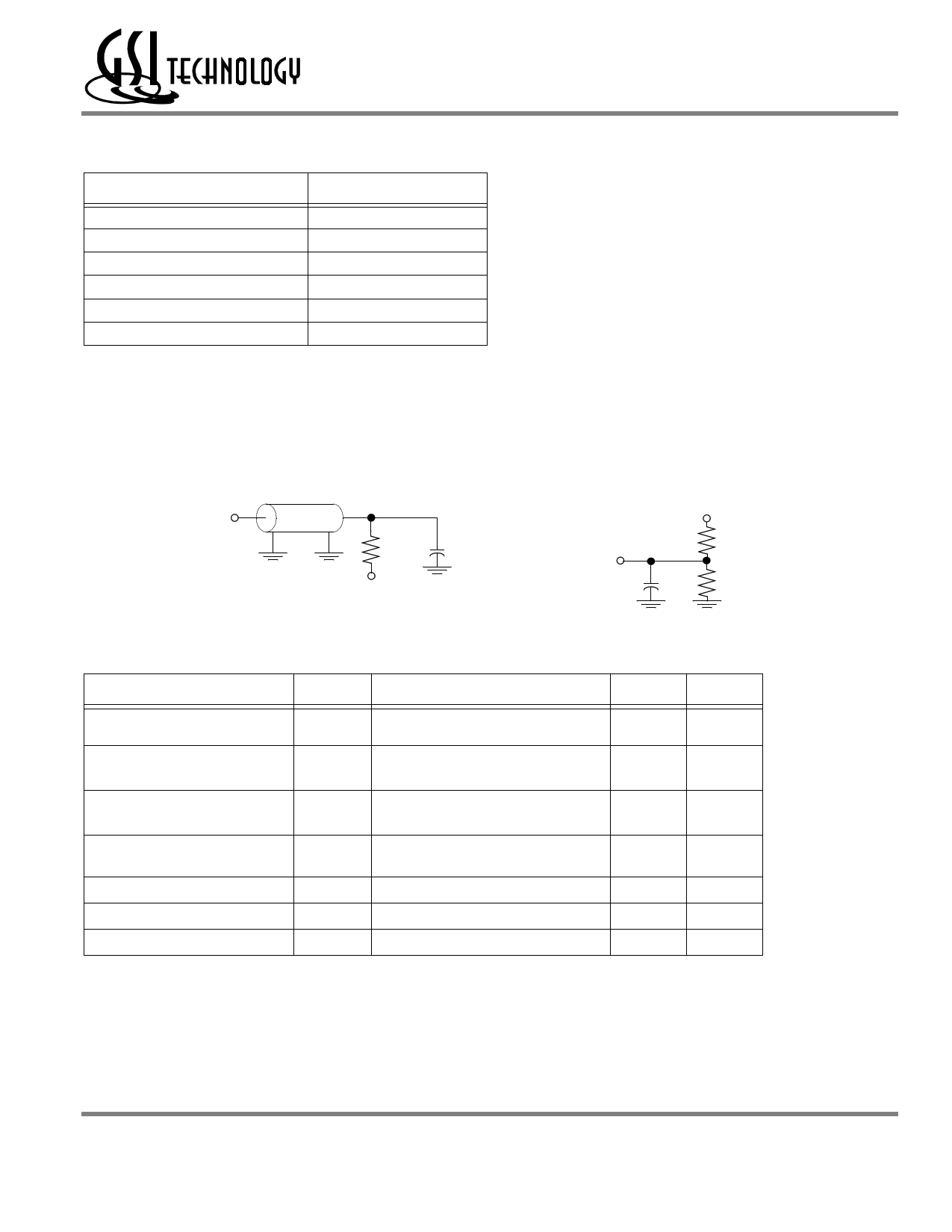

AC Test Conditions

Parameter

Conditions

Input high level

2.3 V

Input low level

0.2 V

Input slew rate

1 V/ns

Input reference level

1.25 V

Output reference level

1.25 V

Output load

Fig. 1& 2

Notes:

1. Include scope and jig capacitance.

2. Test conditions as specified with output loading as shown in Fig. 1 unless otherwise noted.

3. Output Load 2 for tLZ, tHZ, tOLZ and tOHZ

4. Device is deselected as defined by the Truth Table.

Output Load 1

DQ

Output Load 2

2.5 V

50Ω 30pF*

DQ 225Ω

VT = 1.25 V

* Distributed Test Jig Capacitance

5pF* 225Ω

DC Electrical Characteristics

Parameter

Input Leakage Current

(except mode pins)

ZZ Input Current

Symbol

IIL

IINZZ

Mode Pin Input Current

IINM

Output Leakage Current

Output High Voltage

Output High Voltage

Output Low Voltage

IOL

VOH

VOH

VOL

Test Conditions

VIN = 0 to VDD

VDD ≥ VIN ≥ VIH

0V ≤ VIN ≤ VIH

VDD ≥ VIN ≥ VIL

0V ≤ VIN ≤ VIL

Output Disable,

VOUT = 0 to VDD

IOH = –4 mA, VDDQ = 2.375 V

IOH = –4 mA, VDDQ = 3.135 V

IOL = 4 mA

Min

–1 uA

–1 uA

–1 uA

–300 uA

–1 uA

–1 uA

1.7 V

2.4 V

Max

1 uA

1 uA

300 uA

1 uA

1 uA

1 uA

0.4 V

Rev: 1.09 7/2002

11/23

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

© 2000, Giga Semiconductor, Inc.

11 Page | ||

| Páginas | Total 23 Páginas | |

| PDF Descargar | [ Datasheet GS82032A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| GS82032 | 64K x 32 2M Synchronous Burst SRAM | ETC |

| GS82032A | 64K x 32 / 2M Synchronous Burst SRAM | GSI Technology |

| GS82032T | 64K x 32 / 2M Synchronous Burst SRAM | GSI Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |