|

|

PDF UPD30181A Data sheet ( Hoja de datos )

| Número de pieza | UPD30181A | |

| Descripción | 64/32 Bit Microcontroller | |

| Fabricantes | NEC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de UPD30181A (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

DATA SHEET

MOS INTEGRATED CIRCUIT

µPD30181A, 30181AY

VR4181ATM

64-/32-BIT MICROPROCESSOR

DESCRIPTION

The µPD30181A and 30181AY (VR4181A), which are high-performance 64-/32-bit microprocessors employing the

RISC (reduced instruction set computer) architecture developed by MIPSTM, are products in the VR SeriesTM of

microprocessors manufactured by NEC.

The VR4181A includes as its CPU the VR4120™ core, an ultra-low-power-consumption core featuring cache

memory, a high-speed product-sum operation unit, and a memory management unit. Other on-chip components

include an LCD controller, CompactFlash controller, USB host/function controller, DMA controller, SDRAM controller,

PWM controller, AC97/I2S audio interface, full-duplex asynchronous serial interface, IrDA interface, I2C serial

interface, keyboard interface, touch panel interface, real-time clock, A/D converter, D/A converter, and other

controllers and interfaces required for battery-driven mobile information devices, fixed compact information devices,

car navigation systems, and compact embedded devices.

Detailed function descriptions are provided in the following user’s manuals. Be sure to read them before

designing.

• VR4181A Hardware User’s Manual (U16049E)

• VR4100 SeriesTM Architecture User’s Manual (U15509E)

FEATURES

{ VR4120 core (64-bit RISC core) on chip as CPU

{ Pipeline clock: 131 MHz

{ Conforms to MIPS III (except for FPU, LL and SC

instructions) and MIPS16 instruction sets

{ Supports MACC and DMACC high-speed product-sum

operation instructions

{ On-chip cache memory

Capacity includes 8 KB instruction cache and 8 KB

data cache

{ Employs a writeback cache

{ Physical addresses: 32 bits

Virtual addresses: 40 bits

{ On-chip 32 double-entry TLB

{ Effective power management using four modes:

Fullspeed, Standby, Suspend, and Hibernate

{ Employs a high-performance internal system bus (T-

bus)

{ DRAM controller supporting 64 Mb, 128 Mb, and 256

Mb SDRAMs

{ External system bus interface supporting ROM, page

ROM, flash memory, SRAM, ISA devices, IDE (ATA)

devices, and SyncFlash™ memory

{ UMA type LCD controller (supports STN and TFT

panels)

{ ExCA register-compatible CompactFlash interface (2

slots)

{ USB host controller (Rev1.1, OHCI Rev1.0)

controller

{ USB function (Rev1.1) controller

{ AC97 and I2S audio interfaces (1 channel each)

{ Clocked serial interface (1 channel)

{ NS16550-compatible serial interface (3 channels)

{ IrDA (SIR) interface (1 channel)

{ I2C bus interfaces (2 channels, µPD30181AY only)

{ PWM controller (3 channels)

{ DMA controller supporting chain mode (4 channels)

{ Keyboard scan interface (supports 8 × 12 key matrix)

{ X-Y coordinate auto scan touch panel interface

{ On-chip A/D converter and D/A converter

{ On-chip watchdog timer unit

{ RTC unit (total of 3 timer and counter channels)

{ On-chip PLL and clock generators

{ Power supplies: 2.5 V for core, 3.3 V for I/O block

{ Package: 240-pin plastic FBGA

The information in this document is subject to change without notice. Before using this document, please

confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for

availability and additional information.

Document No. U16277EJ1V0DS00 (1st edition)

Date Published October 2002 N CP(K)

Printed in Japan

The mark shows major revised points.

©

©

2002

1997

1 page

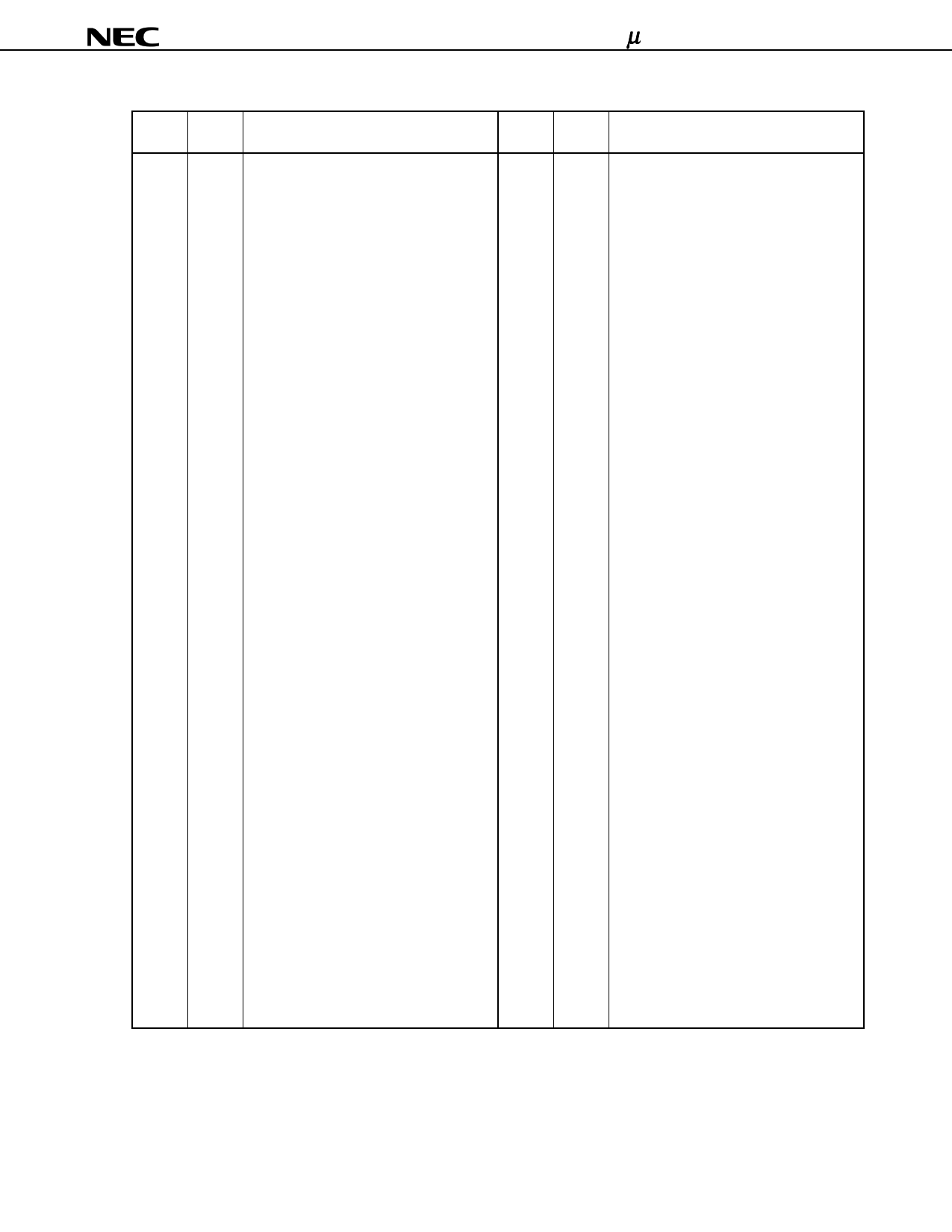

µPD30181A, 30181AY

No. Power

Supply

Name

No. Power

Supply

Name

(3/3)

P10 2.5 V GND2

P11 3.3 V GND3

T16 3.3 V FPD2

T17 3.3 V I.C. (GND3)Note 2

P15 3.3 V CF0_CE2#/GPIO32

T18 3.3 V CF0_EN#/GPIO26

P16 3.3 V CF0_DIR/GPIO27

U1 3.3 V MPOWER

P17 3.3 V CF0_READY/GPIO29

U2 3.3 V AIN0

P18 3.3 V CF0_CE1#/GPIO31

U3 3.3 V TPX0

R1 3.3 V DRQ0#

R2 3.3 V POWER

R3 3.3 V RSTSW#

U4 3.3 V TPY0

U5 3.3 V TxD0/CLKSEL2Note 1

U6 3.3 V RTS0#/GPIO19/CLKSEL1Note 1

R4 3.3 V GNDTP

U7 3.3 V RxD2/IRDIN

R5 3.3 V VDDTP

R6 3.3 V VDDAD

U8 3.3 V CTS2#/BITCLK/SCLK

U9 3.3 V I.C. (GND3)Note 2

R7 3.3 V VDD3

R8 3.3 V GND3

U10 3.3 V SCL0/KPORT7/GPIO12

U11

3.3 V VSYNC/FLM/BMODE1Note 1

R9 3.3 V DCD2#/SDATAIN/SDI

U12 3.3 V FPD15/CF1_READY/GPIO51

R10 3.3 V SDA0/KPORT6/GPIO11

U13 3.3 V FPD12/CF1_CE1#/GPIO48

R11 3.3 V VPBIAS/GPO63

U14 3.3 V FPD10/CF1_CD1#/GPIO46

R12 3.3 V VPLCD/GPO62

U15 3.3 V FPD6/GPIO42

R13 3.3 V VDD3

R14 2.5 V VDD2

U16 3.3 V FPD4/GPIO40

U17

3.3 V CF1_RESET/DBUS32Note 1

R15 3.3 V GND3

U18 3.3 V CF0_VCCEN#/GPIO24

R16 3.3 V CF_REG#/GPIO25

V1 3.3 V TPY1

R17 3.3 V CF0_RESET/GPIO28

V2 3.3 V AIN1

R18 3.3 V CF0_STSCHG#/GPIO30

V3 3.3 V AIN3

T1 3.3 V RTCRST#

V4 3.3 V AOUT

T2 3.3 V POWERON

V5 3.3 V RxD0

T3 3.3 V DAK0#

T4 3.3 V TPX1

T5 3.3 V AIN2

V6 3.3 V CTS0#/GPIO18

V7 3.3 V DTR0#/RTS1#/GPIO17/CLKSEL0Note 1

V8 3.3 V TxD2/IRDOUT/MIPS16ENNote 1

T6 3.3 V DCD0#/GPIO16

V9 3.3 V DSR2#/SRESET#

T7 3.3 V DSR0#/CTS1#/GPIO15

T8 3.3 V RTS2#/SYNC/WS/DIVMODE1Note 1

T9 3.3 V DTR2#/SDATAOUT/SDO/DIVMODE0Note 1

V10 3.3 V RxD1/SCL1/GPIO14

V11 3.3 V DCLK/SHCLK

V12 3.3 V HSYNC/LOCLK/NWIREENNote 1

T10 3.3 V TxD1/SDA1/GPIO13

T11 3.3 V ENAB/M/BMODE0Note 1

V13 3.3 V FPD11/CF1_CD2#/GPIO47

V14 3.3 V FPD9/GPIO45

T12 3.3 V FPD14/CF1_STSCHG#/GPIO50

V15 3.3 V FPD7/GPIO43

T13 3.3 V FPD13/CF1_CE2#/GPIO49

V16 3.3 V FPD5/GPIO41

T14 3.3 V FPD8/GPIO44

V17 3.3 V FPD3

T15 3.3V FPD0

V18 3.3 V FPD1

Notes 1. These pins are used for mode settings. A mode setting is made according to the status of these pins

at the rising edge of the RTCRST# signal. Use pull-up/pull-down resistors to set the pin statuses.

2. Be sure to connect these pins to GND3.

Remark # indicates active low.

Data Sheet U16277EJ1V0DS

5

5 Page

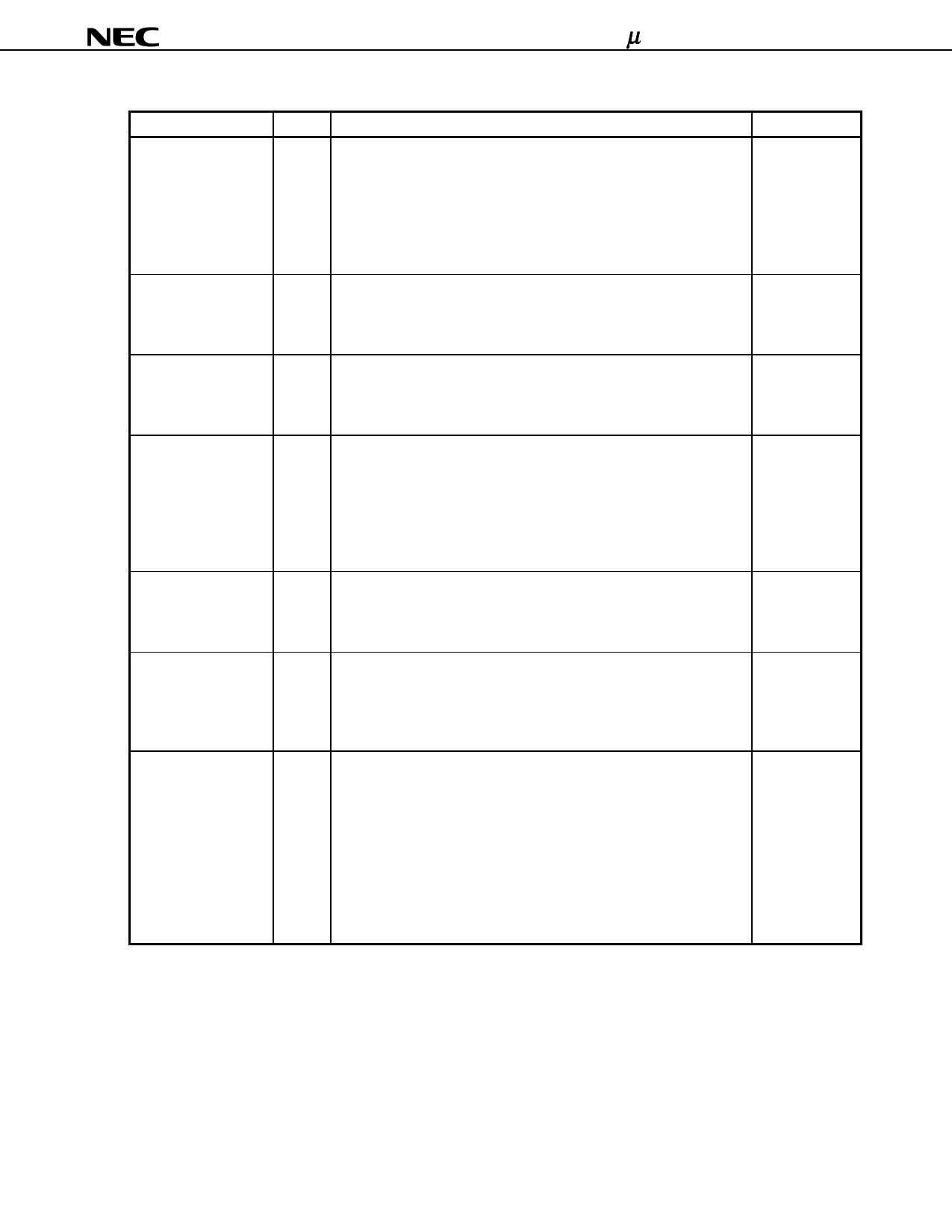

Signal Name

MEMWR#

IORD#

IOWR#

IORDY

IOCS16#

UBE#

LBE(3:0)#

µPD30181A, 30181AY

(2/3)

I/O

Function

Alternate Function

O System bus memory write

This pin becomes active when the VR4181A writes to any of the following

devices.

• ROM, flash memory, SRAM, or general-purpose devices controlled by

the ROMCS# pin or PCS# pin

• External ISA bus memory space devices and CompactFlash/PC Card

memory space devices

–

O System bus I/O read

This pin becomes active when the VR4181A reads data from the external

ISA bus I/O space devices or CompactFlash/PC Card I/O ports. It is

valid only when accessing the external ISA bus I/O space.

–

O System bus I/O write

This pin becomes active when the VR4181A writes data to external ISA

bus I/O space devices or CompactFlash/PC Card I/O ports. It is valid

only when accessing the external ISA bus I/O space.

–

I System bus I/O channel ready

This pin (IORDY) is set as inactive in relation to read/write strobes from

the VR4181A in order to extend the access time for a device connected to

the system bus. It is set as active once the device is in a mode that

supports access from the VR4181A. It can be used to access a device

connected to the ROMCS# pin or PCS# pin or a device connected to the

external ISA space.

–

I System bus sizing request

Set this signal as active when an ISA device connected to the system

bus accesses data in 16-bit width. Bus sizing that uses this pin IOCS16#

is enabled only when accessing the external ISA space.

–

O System bus higher byte enable

This pin becomes active during system bus access if the higher bytes of

the 16-bit data bus are valid. It can be used if a device connected to the

ROMCS# or PCS# pin or a device connected to the external ISA space

uses 16-bit width.

–

O System bus byte enable

The LBE(3:0)# signal pins used for 32-bit general-purpose devices are

shared as the DQM(3:0) signal pins for SDRAM and SyncFlash memory,

so the function of this pin changes based on time division. When the

VR4181A accesses a device that uses the ROMCS# pin or PCS# pin, the

LBE(3:0)# signals become valid only when the SYSEN# signal is at low

level. This signal indicates the data bus’s valid byte lane. If the device

connected to the ROMCS# pin or PCS# pin has 32-bit width, this pin can

be used. When the SYSEN# pin is at high level, this pin operates as the

DQM(3:0) pins that are referenced by SDRAM.

DQM(3:0)

Data Sheet U16277EJ1V0DS

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet UPD30181A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| UPD30181 | 64/32 Bit Microcontroller | NEC |

| UPD30181A | 64/32 Bit Microcontroller | NEC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |