|

|

PDF 74F189SJ Data sheet ( Hoja de datos )

| Número de pieza | 74F189SJ | |

| Descripción | 64-Bit Random Access Memory with 3-STATE Outputs | |

| Fabricantes | Fairchild | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de 74F189SJ (archivo pdf) en la parte inferior de esta página. Total 7 Páginas | ||

|

No Preview Available !

April 1988

Revised July 1999

74F190

Up/Down Decade Counter with Preset and Ripple Clock

General Description

The 74F190 is a reversible BCD (8421) decade counter

featuring synchronous counting and asynchronous preset-

ting. The preset feature allows the 74F190 to be used in

programmable dividers. The Count Enable input, the Termi-

nal Count output and the Ripple Clock output make possi-

ble a variety of methods of implementing multistage

counters. In the counting modes, state changes are initi-

ated by the rising edge of the clock.

Features

s High-speed—125 MHz typical count frequency

s Synchronous counting

s Asynchronous parallel load

s Cascadable

Ordering Code:

Order Number Package Number

Package Description

74F190SC

M16A

16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

74F190PC

N16E

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

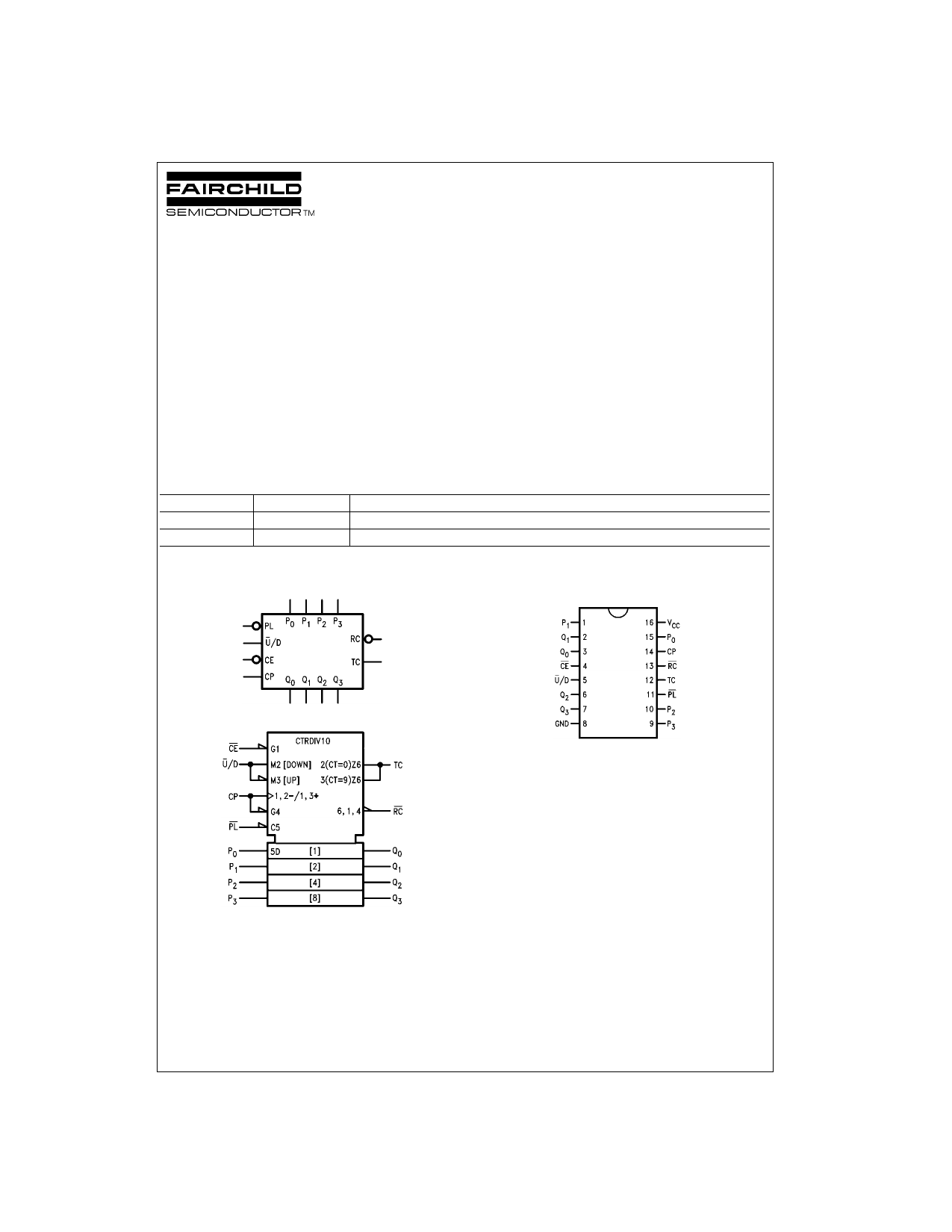

Logic Symbols

Connection Diagram

IEEE/IEC

© 1999 Fairchild Semiconductor Corporation DS009494

www.fairchildsemi.com

1 page

AC Electrical Characteristics

Symbol

Parameter

fMAX

tPLH

tPHL

tPLH

tPHL

tPLH

tPHL

tPLH

tPHL

tPLH

tPHL

tPLH

tPHL

tPLH

tPHL

tPLH

tPHL

Maximum Clock Frequency

Propagation Delay

CP to Qn

Propagation Delay

CP to TC

Propagation Delay

CP to RC

Propagation Delay

CE to RC

Propagation Delay

U /D to RC

Propagation Delay

U /D to TC

Propagation Delay

Pn to Qn

Propagation Delay

PL to Qn

TA = +25°C

VCC = +5.0V

CL = 50 pF

Min Typ Max

100 125

3.0 5.5 7.5

5.0 8.5 11.0

6.0

10.0

13.0

5.0 8.5 11.0

3.0 5.5 7.5

3.0 5.0 7.0

3.0 5.0 7.0

3.0 5.5 7.0

7.0 11.0 18.0

5.5 9.0 12.0

4.0 7.0 10.0

4.0 6.5 10.0

3.0 4.5 7.0

6.0

10.0

13.0

5.0 8.5 11.0

5.5 9.0 12.0

AC Operating Requirements

Symbol

Parameter

tS(H)

tS(L)

tH(H)

tH(L)

tS(L)

tH(L)

tS(H)

tS(L)

tH(H)

tH(L)

tW(L)

tW(L)

tREC

Setup Time, HIGH or LOW

Pn to PL

Hold Time, HIGH or LOW

Pn to PL

Setup Time, LOW

CE to CP

Hold Time, LOW

CE to CP

Setup Time, HIGH or LOW

U /D to CP

Hold Time, HIGH or LOW

U /D to CP

PL Pulse Width, LOW

CP Pulse Width, LOW

Recovery Time PL to CP

TA = +25°C

VCC = +5.0V

Min Max

4.5

4.5

2.0

2.0

10.0

0

12.0

12.0

0

0

6.0

5.0

6.0

TA −55°C to +125°C

VCC = +5.0V

CL = 50 pF

Min Max

75

3.0 9.5

5.0 13.5

6.0 16.5

5.0 13.5

3.0 9.5

3.0 9.0

3.0 9.0

3.0 9.0

7.0 22.0

5.5 14.0

4.0 13.5

4.0 12.5

3.0 9.0

6.0 16.0

5.0 13.0

5.5 14.5

TA = 0°C to +70°C

VCC = +5.0V

CL = 50 pF

Min Max

90

3.0 8.5

5.0 12.0

6.0 14.0

5.0 12.0

3.0 8.5

3.0 8.0

3.0 8.0

3.0 8.0

7.0 20.0

5.5 13.0

4.0 11.0

4.0 11.0

3.0 8.0

6.0 14.0

5.0 12.0

5.5 13.0

TA −55°C to +125°C

VCC = +5.0V

Min Max

6.0

6.0

2.0

2.0

10.5

TA = 0°C to +70°C

VCC = +5.0V

Min Max

5.0

5.0

2.0

2.0

10.0

00

12.0

12.0

0

0

8.5

7.0

7.5

12.0

12.0

0

0

6.0

5.0

6.0

Units

MHz

ns

ns

ns

ns

ns

Units

ns

ns

ns

ns

ns

ns

5 www.fairchildsemi.com

5 Page | ||

| Páginas | Total 7 Páginas | |

| PDF Descargar | [ Datasheet 74F189SJ.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 74F189SC | 64-Bit Random Access Memory with 3-STATE Outputs | Fairchild |

| 74F189SC | 64-Bit Random Access Memory with TRI-STATEE Outputs | National |

| 74F189SJ | 64-Bit Random Access Memory with TRI-STATEE Outputs | National |

| 74F189SJ | 64-Bit Random Access Memory with 3-STATE Outputs | Fairchild |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |