|

|

PDF 7C199-25 Data sheet ( Hoja de datos )

| Número de pieza | 7C199-25 | |

| Descripción | 32K x 8 Static RAM | |

| Fabricantes | Cypress Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de 7C199-25 (archivo pdf) en la parte inferior de esta página. Total 13 Páginas | ||

|

No Preview Available !

CY7C199

Features

• High speed

— 10 ns

• Fast tDOE

• CMOS for optimum speed/power

• Low active power

— 467 mW (max, 12 ns “L” version)

• Low standby power

— 0.275 mW (max, “L” version)

• 2V data retention (“L” version only)

• Easy memory expansion with CE and OE features

• TTL-compatible inputs and outputs

• Automatic power-down when deselected

Functional Description

The CY7C199 is a high-performance CMOS static RAM

organized as 32,768 words by 8 bits. Easy memory expansion

Logic Block Diagram

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

CE

WE

OE

INPUT BUFFER

1024 x 32 x 8

ARRAY

COLUMN

DECODER

POWER

DOWN

32K x 8 Static RAM

is provided by an active LOW Chip Enable (CE) and active

LOW Output Enable (OE) and three-state drivers. This device

has an automatic power-down feature, reducing the power

consumption by 81% when deselected. The CY7C199 is in the

standard 300-mil-wide DIP, SOJ, and LCC packages.

An active LOW Write Enable signal (WE) controls the

writing/reading operation of the memory. When CE and WE

inputs are both LOW, data on the eight data input/output pins

(I/O0 through I/O7) is written into the memory location

addressed by the address present on the address pins (A0

through A14). Reading the device is accomplished by selecting

the device and enabling the outputs, CE and OE active LOW,

while WE remains inactive or HIGH. Under these conditions,

the contents of the location addressed by the information on

address pins are present on the eight data input/output pins.

The input/output pins remain in a high-impedance state unless

the chip is selected, outputs are enabled, and Write Enable

(WE) is HIGH. A die coat is used to improve alpha immunity.

I/O0

I/O1

I/O2

I/O3

I/O4

I/O5

I/O6

I/O7

Pin Configurations

DIP / SOJ / SOIC

Top View

LCC

Top View

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

I/O0

I/O1

I/O2

GND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28 VCC

27 WE

26 A4

25 A3

24 A2

23 A1

22 OE

21 A0

20 CE

19 I/O7

18 I/O6

17 I/O5

16 I/O4

15 I/O3

3 2 1 28 27

A8 4

A9 5

26 A4

25 A3

A10 6

A11 7

A12 8

24 A2

23 A1

22 OE

A13 9

A14 10

21 A0

20 CE

I/O0 11

19 I/O7

I/O1 12

18 I/O6

1314151617

OE

A1

A2

A3

A4

WE

V CC

A5

A6

A7

A8

A9

A 10

A 11

22

23

24

25

26

27

28

1

2

3

4

5

6

7

TSOP I

Top View

(not to scale)

21 A 0

20 CE

19 I/O 7

18 I/O 6

17 I/O 5

16 I/O 4

15 I/O 3

14 GND

13 I/O 2

12 I/O 1

11 I/O 0

10 A 14

9 A 13

8 A 12

Selection Guide

Maximum Access Time

Maximum Operating Current

L

Maximum CMOS Standby Current

L

Shaded area contains advance information.

7C199

-8

8

120

0.5

7C199

-10

10

110

90

0.5

0.05

7C199

-12

12

160

90

10

0.05

7C199

-15

15

155

90

10

0.05

7C199

-20

20

150

90

10

0.05

7C199

-25

25

150

80

10

0.05

7C199

-35

35

140

70

10

0.05

7C199

-45

45

140

Unit

ns

mA

10 mA

Cypress Semiconductor Corporation • 3901 North First Street • San Jose, CA 95134 • 408-943-2600

Document #: 38-05160 Rev. *A

Revised January 7, 2003

1 page

CY7C199

Switching Characteristics Over the Operating Range (-20, -25, -35, -45)[3, 7]

Parameter

Description

tPD CE HIGH to Power-down

Write Cycle[10,11]

tWC

tSCE

tAW

tHA

tSA

tPWE

tSD

tHD

tHZWE

tLZWE

Write Cycle Time

CE LOW to Write End

Address Set-up to Write End

Address Hold from Write End

Address Set-up to Write Start

WE Pulse Width

Data Set-up to Write End

Data Hold from Write End

WE LOW to High-Z[9]

WE HIGH to Low-Z[8]

7C199-20

Min. Max.

20

7C199-25

Min. Max.

20

20 25

15 18

15 20

00

00

15 18

10 10

00

10 11

33

7C199-35

Min. Max.

20

35

22

30

0

0

22

15

0

15

3

7C199-45

Min. Max.

25

45

22

40

0

0

22

15

0

15

3

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Switching Waveforms

Read Cycle No. 1[12, 13]

ADDRESS

DATA OUT

tOHA

PREVIOUS DATA VALID

Read Cycle No. 2 [13, 14]

CE

tAA

tRC

tRC

DATA VALID

tACE

OE

DATA OUT

tDOE

tLZOE

HIGH IMPEDANCE

tLZCE

VCC

SUPPLY

CURRENT

tPU

50%

Notes:

12. Device is continuously selected. OE, CE = VIL.

13. WE is HIGH for read cycle.

14. Address valid prior to or coincident with CE transition LOW.

DATA VALID

tHZOE

tHZCE

HIGH

IMPEDANCE

tPD

50%

ICC

ISB

Document #: 38-05160 Rev. *A

Page 5 of 13

5 Page

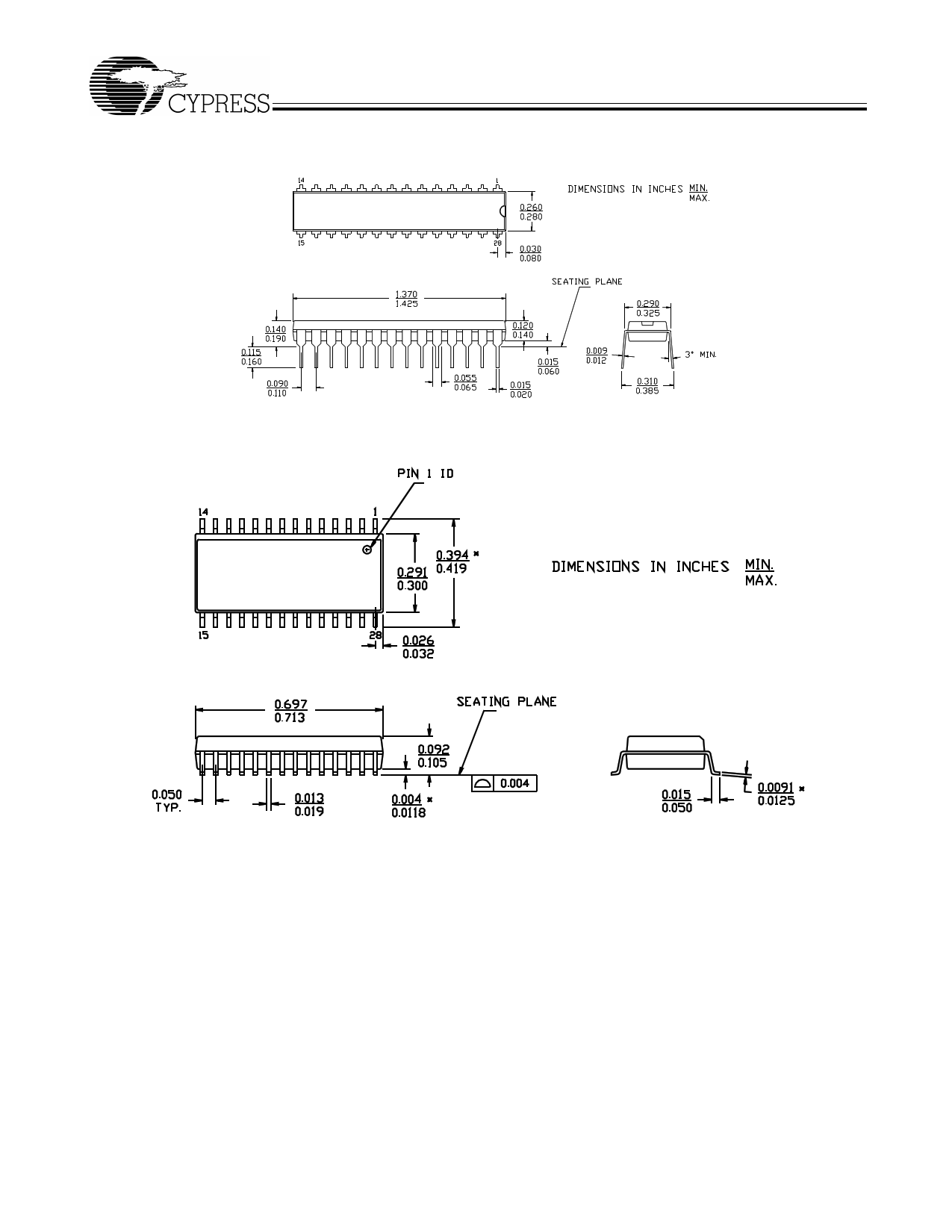

Package Diagrams (continued)

28-pin (300-Mil) Molded DIP P21

CY7C199

28-pin (300-Mil) Molded SOIC S21

51-85014-B

Document #: 38-05160 Rev. *A

51-85026-A

Page 11 of 13

11 Page | ||

| Páginas | Total 13 Páginas | |

| PDF Descargar | [ Datasheet 7C199-25.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 7C199-20 | 32K x 8 Static RAM | Cypress Semiconductor |

| 7C199-25 | 32K x 8 Static RAM | Cypress Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |