|

|

PDF 74LVT373DB Data sheet ( Hoja de datos )

| Número de pieza | 74LVT373DB | |

| Descripción | 3.3 Volt ABT octal transparent latch 3-State | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de 74LVT373DB (archivo pdf) en la parte inferior de esta página. Total 6 Páginas | ||

|

No Preview Available !

Philips Semiconductors Low Voltage Products

3.3 Volt ABT octal transparent latch (3–State)

Objective specification

74LVT373

FEATURES

• Designed for use in the 3.3V

high–performance market

• Supports mixed–mode signal operation; 5V

input and output voltages with 3.3V VCC

• Bus–hold inputs eliminate the need for

external pull-up resistors to hold unused

pins

• Live insertion/extraction permitted

• No bus current loading when output is tied

to 5V bus

• 8–bit transparent latch

• 3-State output buffers

• Zero-static power dissipation

• Pin and function compatibility with ABT

• AC and DC performance compatibility with

ABT

• Latch–up protection exceeds 500mA per

JEDEC JC40.2 Std 17

• ESD protection exceeds 2000 V per MIL

STD 883 Method 3015 and 200 V per

Machine Model

DESCRIPTION

The 74LVT373 device is designed specifically

for low–voltage (3.3V) VCC operation, but can

provide a TTL interface to a 5V system

environment.

The 74LVT373 high-performance BiCMOS

device combines zero static and low dynamic

power dissipation with high speed and high

output drive.

The 74LVT373 device is an octal transparent

latch coupled to eight 3-State output buffers.

The two sections of the device are controlled

independently by Enable (E) and Output

Enable (OE) control gates.

The data on the D inputs are transferred to

the latch outputs when the Latch Enable (E)

input is High. The latch remains transparent

to the data inputs while E is High, and stores

the data that is present one setup time before

the High-to-Low enable transition.

The 3-State output buffers are designed to

drive heavily loaded 3-State buses, MOS

memories, or MOS microprocessors. The

active-Low Output Enable (OE) controls all

eight 3-State buffers independent of the latch

operation.

When OE is Low, the latched or transparent

data appears at the outputs. When OE is

High, the outputs are in the High-impedance

”OFF” state, which means they will neither

drive nor load the bus.

QUICK REFERENCE DATA

SYMBOL

PARAMETER

tPLH

tPHL

CIN

COUT

ICCZ

Propagation delay

Dn to Qn

Input capacitance

Output capacitance

Total supply current

CONDITIONS

Tamb = 25°C; GND = 0V

CL = 50pF; VCC = 5V

VI = 0V or VCC

VI = 0V or VCC

Outputs disabled; VCC =5.5V

TYPICAL

4.2

4

7

50

UNIT

ns

pF

pF

µA

ORDERING INFORMATION

PACKAGES

20–Pin Plastic SOL

20–Pin Plastic SSOP

20–Pin Plastic TSSOP

TEMPERATURE RANGE

-40°C to +85°C

-40°C to +85°C

-40°C to +85°C

ORDER CODE

74LVT373D

74LVT373DB

74LVT373PW

PIN DESCRIPTION

PIN NUMBER

1

3, 4, 7, 8, 13, 14, 17, 18

2, 5, 6, 9, 12, 15, 16, 19

11

10

20

SYMBOL

OE

D0-D7

Q0-Q7

E

GND

VCC

Output enable input (active-Low)

Data inputs

Data outputs

Enable input (active-High)

Ground (0V)

Positive supply voltage

FUNCTION

DRAWING NUMBER

0172D

1640B

TBD

July 1993

2

1 page

Philips Semiconductors Low Voltage Products

3.3 Volt ABT octal transparent latch (3–State)

Objective specification

74LVT373

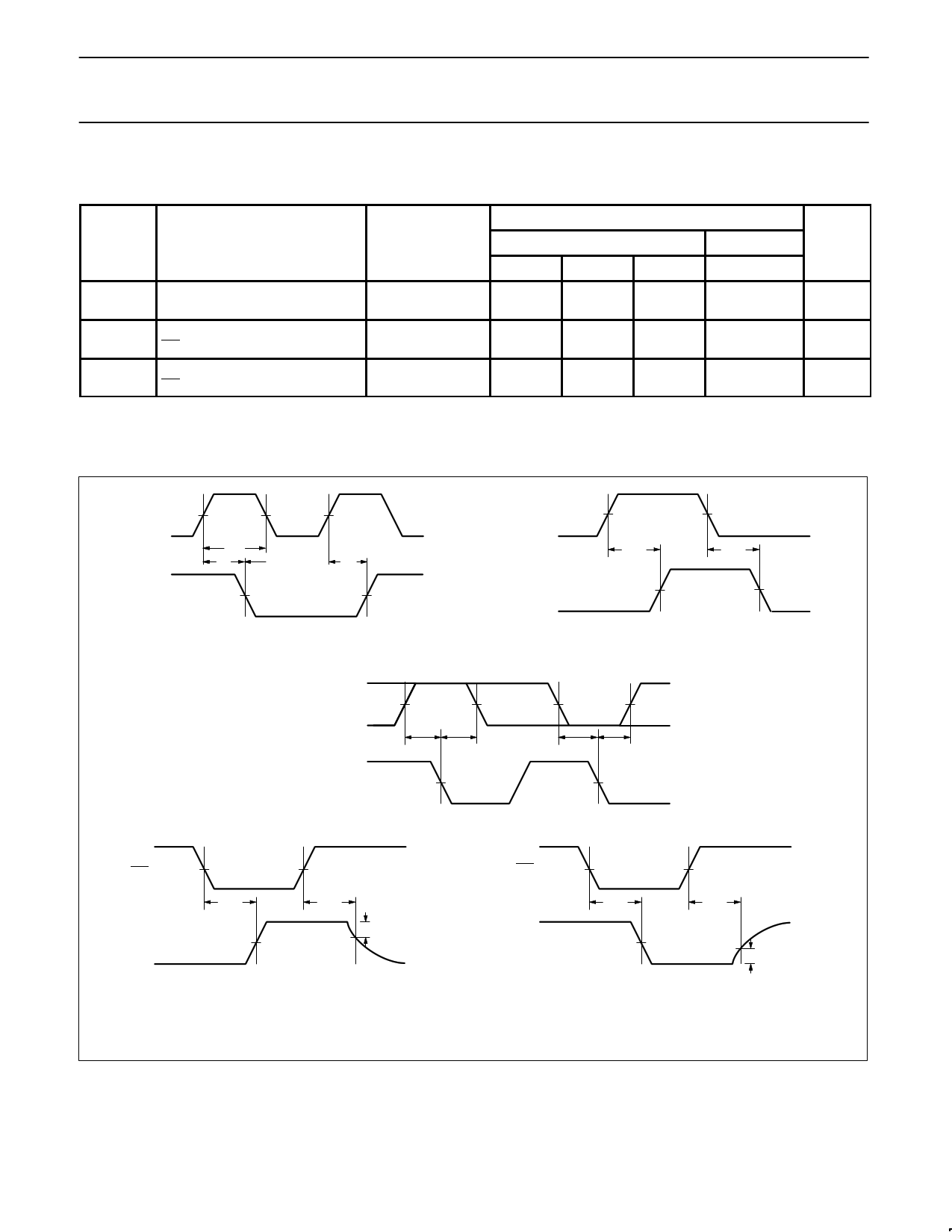

AC CHARACTERISTICS

GND = 0V; tR = tF = 6ns; CL = 50pF; RL = 500Ω, Tamb = –40°C to +85°C.

SYMBOL

PARAMETER

WAVEFORM

tPLH Propagation delay

tPHL

An to Yn

NO TAG

tPZH

tPZL

Output enable time

OEn to Yn

NO TAG

tPHZ

tPLZ

Output disable time

OEn to Yn

NO TAG

NOTE:

1. All typical values are at VCC = 3.3V and Tamb = 25°C.

AC WAVEFORMS

VM = 1.5V, VIN = GND to 3.0V

LIMITS

VCC = 3.3V ±0.3V

MIN

TYP1

MAX

2.7

2.9

3.4

3.4

3.7

2.6

VCC = 2.7V

MAX

UNIT

ns

ns

ns

E VM

VM VM

Dn VM VM

tw(H)

tPHL

tPLH

Qn VM

VM

ÉÉÉWaveform 1. Propagation Delay, Enable to

Output, and Enable Pulse Width

ÉÉÉÉÉÉÉÉÉÉÉÉDn VM

ts(H)

tPLH

tPHL

Qn VM VM

ÉÉÉÉÉÉÉÉÉÉWaveform 2. Propagation Delay for Data

to Outputs

ÉÉÉÉÉÉÉÉÉÉÉÉÉÉÉÉÉÉÉÉÉÉÉÉÉÉÉÉÉÉÉÉÉÉÉÉÉÉÉÉVM VM VM

th(H)

ts(L)

th(L)

E VM

VM

Waveform 3. Data Setup and Hold Times

OE VM VM

tPZH

tPHZ

Qn

VOH –0.3V

VM

0V

Waveform 4. 3-State Output Enable Time to High Level

and Output Disable Time from High Level

OE VM VM

tPZL

tPLZ

Qn VM VOL +0.3V

0V

Waveform 5. 3-State Output Enable Time to Low Level

and Output Disable Time from Low Level

NOTE: The shaded areas indicate when the input is permitted to change for predictable output performance.

July 1993

6

5 Page | ||

| Páginas | Total 6 Páginas | |

| PDF Descargar | [ Datasheet 74LVT373DB.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 74LVT373D | 3.3 Volt ABT octal transparent latch 3-State | NXP Semiconductors |

| 74LVT373DB | 3.3 Volt ABT octal transparent latch 3-State | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |