|

|

PDF FAN1654 Data sheet ( Hoja de datos )

| Número de pieza | FAN1654 | |

| Descripción | 1.5A LDO/ DDR Bus Termination Regulator | |

| Fabricantes | Fairchild Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de FAN1654 (archivo pdf) en la parte inferior de esta página. Total 7 Páginas | ||

|

No Preview Available !

www.fairchildsemi.com

FAN1654

1.5A LDO, DDR Bus Termination Regulator

Features

• Sinks and sources 1A continuous, 1.5A peak

• -40°C to +125°C Operating Range

• Load regulation: (VDDQ/2) ± 40mV

• 5mA VREF buffer tracks VTT

• On-chip thermal limiting

• Power-enhanced eTSSOP™-16 package

• Low Current Shutdown Mode

• Output Short Circuit Protection

Applications

• DDR terminators

Description

The FAN1654 is a low-cost bi-directional LDO specifically

designed for terminating DDR memory bus. It can both sink

and source up to 1A continuous, 1.5A peak, providing

enough current for most DDR applications. Load regulation

meets the JEDEC spec, VTT = (VDDQ/2) ± 40mV.

The FAN1654 includes a buffered reference voltage capable

of supplying up to 5mA current. On-chip thermal limiting

provides protection against a combination of power overload

and ambient temperature that would create an excessive

junction temperature. A shutdown input puts the FAN1654

into a low power mode for laptop computer applications.

The FAN1654 regulator is available in a power-enhanced

eTSSOP™-16 package, and the standard SOIC-14

Block Diagram

VDDQ

VDD

VDD VDD SHDN

VREFOUT

VREFIN

200k

-

+

+

200k

FAN1655

VSSQ

-

VSS VSS VSS

VTTFORCE

VTTFORCE

VTTSENSE

REV. 1.0.5 4/17/02

1 page

FAN1654

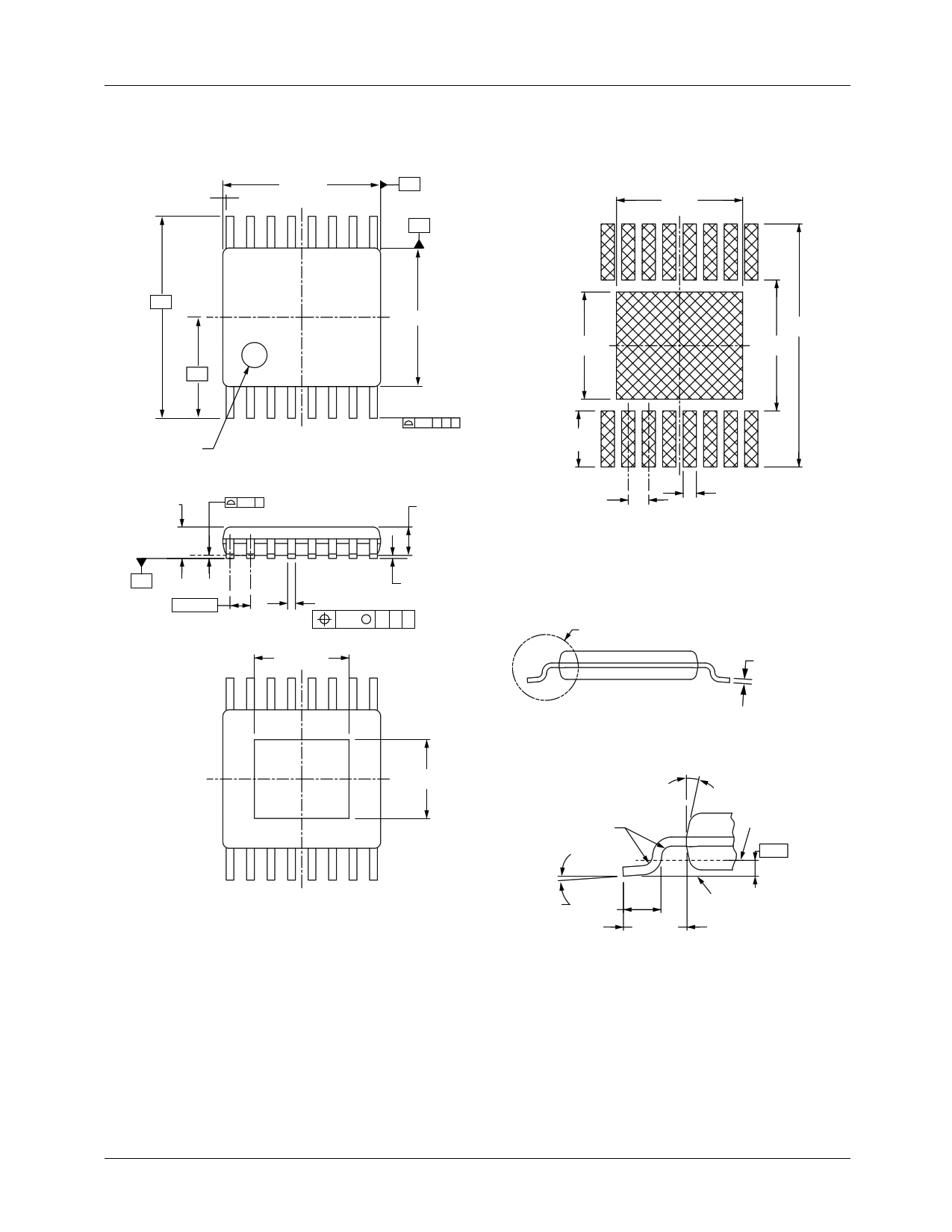

Mechanical Dimensions

16 Lead eTSSOP

0.10 TYP

16

5.0 ± 0.1

-A-

9

-B-

6.4

3.2

PIN #1 IDENT.

1

1.2 MAX

ALL LEAD TIPS

0.1 C

4.4 ± 0.1

8 0.2 C B A

ALL LEAD TIPS

(0.90)+–00..1105

-C-

0.65 TYP

9

0.10±0.05 TYP

(0.19–0.30)

0.10 M C B A

1.7 MIN

16

PRODUCT SPECIFICATION

4.00

16 9

3.40

7.72

4.16

(1.78)

1

0.65 TYP

8

0.42 TYP

LAND PATTERN RECOMMENDATION

SEE DETAIL A

(0.09–0.20)

1.5 MIN

81

BOTTOM VIEW

NOTES:

A. CONFORMS TO JEDEC REGISTRATION MO-153, VARIATION ABT,

DATED 10/97.

B. DIMENSIONS ARE IN MILLIMETERS.

C. DIMENSIONS ARE EXCLUSIVE OF BURRS, MOLD FLASH,

AND THE BAR EXTENSIONS.

D. DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994.

R0.09MIN

0°–8°

12° TOP & BOTTOM

GAGE PLANE

0.25

0.75

0.45

SEATING PLANE

(1.00)

DETAIL A

REV. 1.0.5 4/17/02

5

5 Page | ||

| Páginas | Total 7 Páginas | |

| PDF Descargar | [ Datasheet FAN1654.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| FAN1654 | 1.5A LDO/ DDR Bus Termination Regulator | Fairchild Semiconductor |

| FAN1655 | 3A DDR Bus Termination Regulator | Fairchild Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |