|

|

PDF ISL6527A Data sheet ( Hoja de datos )

| Número de pieza | ISL6527A | |

| Descripción | Single Synchronous Buck Pulse-Width Modulation (PWM) Controller | |

| Fabricantes | Intersil | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ISL6527A (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

Data Sheet

ISL6527, ISL6527A

September 29, 2015

FN9056.11

Single Synchronous Buck Pulse-Width

Modulation (PWM) Controller

The ISL6527, ISL6527A make simple work out of

implementing a complete control and protection scheme for

a DC/DC step-down converter. Designed to drive N-Channel

MOSFETs in a synchronous buck topology, the ISL6527,

ISL6527A integrate the control, output adjustment,

monitoring and protection functions into a single package.

The ISL6527, ISL6527A provide simple, single feedback loop,

voltage-mode control with fast transient response. The output

voltage can be regulated to as low as the provided external

reference. A fixed frequency oscillator reduces design

complexity, while balancing typical application cost and

efficiency.

The error amplifier features a 15MHz gain-bandwidth

product and 6V/µs slew rate, which enables high converter

bandwidth for fast transient performance. The resulting

PWM duty cycles range from 0% to 100%.

Protection from overcurrent conditions is provided by

monitoring the rDS(ON) of the upper MOSFET to inhibit PWM

operation appropriately. This approach simplifies the

implementation and improves efficiency by eliminating the

need for a current sense resistor.

Features

• Operates from 3.3V to 5V Input

• Utilizes an External Reference

• Drives N-Channel MOSFETs

• Simple Single-Loop Control Design

- Voltage-Mode PWM Control

• Fast Transient Response

- High Bandwidth Error Amplifier

- Full 0% to 100% Duty Cycle

• Lossless, Programmable Overcurrent Protection

- Uses Upper MOSFET’s rDS(ON)

• Converter Can Source and Sink Current

• Small Converter Size

- Internal Fixed Frequency Oscillator

- ISL6527: 300kHz

- ISL6527A: 600kHz

• Internal Soft-Start

• 14 Ld SOIC or 16 Ld 5x5 QFN

• QFN package:

- Compliant to JEDEC PUB95 MO-220 QFN - Quad Flat

No Leads - Package Outline

- Near Chip-Scale Package Footprint, which Improves

PCB Efficiency and has a Thinner Profile

• Pb-Free (RoHS compliant)

Applications

• Power Supplies for Microprocessors

- PCs

- Embedded Controllers

• Subsystem Power Supplies

- PCI/AGP/GTL+ Busses

- ACPI Power Control

- DDR SDRAM Bus Termination Supply

• Cable Modems, Set-Top Boxes, and DSL Modems

• DSP and Core Communications Processor Supplies

• Memory Supplies

• Personal Computer Peripherals

• Industrial Power Supplies

• 3.3V Input DC/DC Regulators

• Low Voltage Distributed Power Supplies

1 CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774 | Copyright Intersil Americas LLC 2003-2008, 2015. All Rights Reserved

Intersil (and design) is a trademark owned by Intersil Corporation or one of its subsidiaries.

All other trademarks mentioned are the property of their respective owners.

1 page

ISL6527, ISL6527A

Functional Pin Description

14 LD (SOIC)

TOP VIEW

GND 1

LGATE 2

CPVOUT 3

CT1 4

CT2 5

OCSET/SD 6

FB 7

14 UGATE

13 BOOT

12 PHASE

11 VCC

10 CPGND

9 REF_IN

8 COMP

16 LD 5X5 (QFN)

TOP VIEW

16 15 14 13

CPVOUT 1

CT1 2

CT2 3

OCSET/SD 4

12 PHASE

11 VCC

10 CPGND

9 NC

5678

VCC

This pin provides the bias supply for the ISL6527, ISL6527A.

Connect a well-decoupled 3.3V supply to this pin.

COMP and FB

COMP and FB are two of the three available external pins of

the error amplifier. The FB pin is the inverting input of the

internal error amplifier and the COMP pin is the error

amplifier output. These pins are used to compensate the

voltage-control feedback loop of the converter.

REF_IN

This pin is the third available external pin of the error

amplifier and represents the non-inverting input to the error

amplifier. Connect the desired reference voltage to this pin.

Voltage applied to this pin must not exceed 1.5V.

GND

This pin represents the signal and power ground for the IC.

Tie this pin to the ground island/plane through the lowest

impedance connection available.

PHASE

Connect this pin to the upper MOSFET’s source. This pin is

used to monitor the voltage drop across the upper MOSFET

for overcurrent protection.

UGATE

Connect this pin to the upper MOSFET’s gate. This pin

provides the PWM-controlled gate drive for the upper

MOSFET. This pin is also monitored by the adaptive

shoot-through protection circuitry to determine when the

upper MOSFET has turned off.

BOOT

This pin provides ground referenced bias voltage to the

upper MOSFET driver. A bootstrap circuit is used to create a

voltage suitable to drive a logic-level N-channel MOSFET.

LGATE

Connect this pin to the lower MOSFET’s gate. This pin

provides the PWM-controlled gate drive for the lower

MOSFET. This pin is also monitored by the adaptive

shoot-through protection circuitry to determine when the

lower MOSFET has turned off.

OCSET/SD

Connect a resistor (ROCSET) from this pin to the drain of the

upper MOSFET (VIN). ROCSET, an internal 20µA current

source (IOCSET), and the upper MOSFET ON-resistance

(rDS(ON)) set the converter overcurrent (OC) trip point

according to Equation 1:

IPEAK = I--O-----C----S---r-E-D---T-S---x---RO-----ON----C----S----E----T--

(EQ. 1)

An overcurrent trip cycles the soft-start function.

Pulling OCSET/SD to a voltage level below 0.8V disables

the controller. Disabling the ISL6527, ISL6527A causes the

oscillator to stop, the LGATE and UGATE outputs to be held

low, and the soft-start circuitry to re-arm.

CT1 and CT2

These pins are the connections for the external charge

pump capacitor. A minimum of a 0.1µF ceramic capacitor is

recommended for proper operation of the IC.

CPVOUT

This pin represents the output of the charge pump. The

voltage at this pin is the bias voltage for the IC. Connect a

decoupling capacitor from this pin to ground. The value of

the decoupling capacitor should be at least 10x the value of

the charge pump capacitor. This pin may be tied to the

bootstrap circuit as the source for creating the BOOT

voltage.

CPGND

This pin represents the signal and power ground for the

charge pump. Tie this pin to the ground island/plane through

the lowest impedance connection available.

5 FN9056.11

September 29, 2015

5 Page

ISL6527, ISL6527A

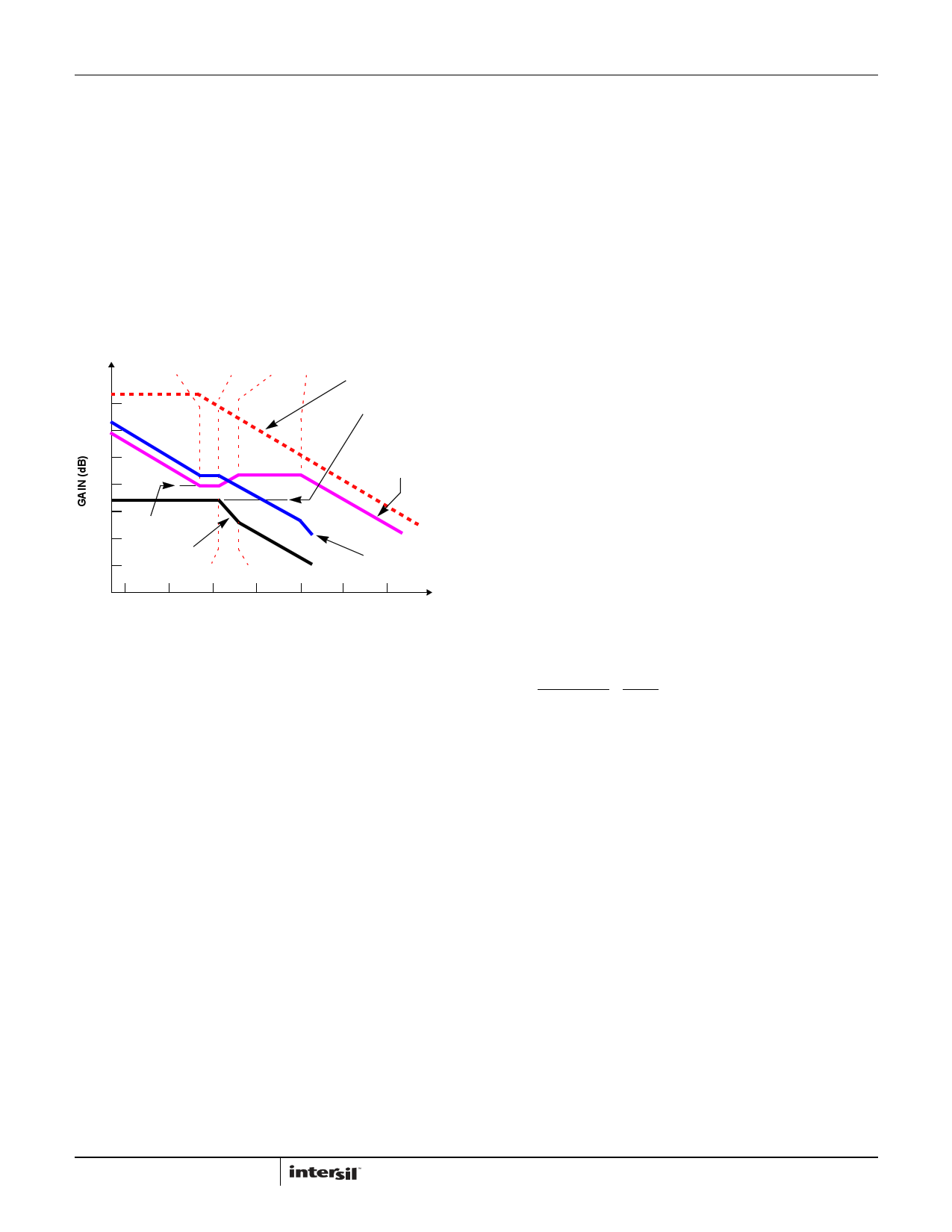

error amplifier gain bounds the compensation gain. Check the

compensation gain at FP2 with the capabilities of the error

amplifier. The closed loop gain is constructed on the graph of

Figure 6 by adding the modulator gain (in dB) to the

compensation gain (in dB). This is equivalent to multiplying

the modulator transfer function to the compensation transfer

function and plotting the gain.

The compensation gain uses external impedance networks

ZFB and ZIN to provide a stable, high bandwidth (BW) overall

loop. A stable control loop has a gain crossing with

-20dB/decade slope and a phase margin greater than 45°.

Include worst-case component variations when determining

phase margin.

FZ1 FZ2 FP1 FP2

OPEN LOOP

100 ERROR AMP GAIN

80

20

log

V----V-O---I--S-N---C---

60

40 COMPENSATION

GAIN

20

0

-20

20 log

RR-----21--

MODULATOR

-40

GAIN

FLC FESR

LOOP GAIN

-60

10 100 1k 10k 100k 1M 10M

FREQUENCY (Hz)

FIGURE 6. ASYMPTOTIC BODE PLOT OF CONVERTER GAIN

Component Selection Guidelines

Charge Pump Capacitor Selection

A capacitor across pins CT1 and CT2 is required to create the

proper bias voltage for the ISL6527, ISL6527A when operating

the IC from 3.3V. Selecting the proper capacitance value is

important so that the bias current draw and the current required

by the MOSFET gates do not overburden the capacitor. A

conservative approach is presented in Equation 11:

CPUMP = I--B----i-V-a---s-C--A--C--n---d----G-f--s-a----t-e-- 1.5

(EQ. 11)

Output Capacitor Selection

An output capacitor is required to filter the output and supply

the load transient current. The filtering requirements are a

function of the switching frequency and the ripple current.

The load transient requirements are a function of the slew

rate (di/dt) and the magnitude of the transient load current.

These requirements are generally met with a mix of

capacitors and careful layout.

Modern digital ICs can produce high transient load slew

rates. High frequency capacitors initially supply the transient

and slow the current load rate seen by the bulk capacitors.

The bulk filter capacitor values are generally determined by

the ESR (Effective Series Resistance) and voltage rating

requirements rather than actual capacitance requirements.

High frequency decoupling capacitors should be placed as

close to the power pins of the load as physically possible. Be

careful not to add inductance in the circuit board wiring that

could cancel the usefulness of these low inductance

components. Consult with the manufacturer of the load on

specific decoupling requirements.

Use only specialized low-ESR capacitors intended for

switching-regulator applications for the bulk capacitors. The

bulk capacitor’s ESR will determine the output ripple voltage

and the initial voltage drop after a high slew-rate transient. An

aluminum electrolytic capacitor’s ESR value is related to the

case size with lower ESR available in larger case sizes.

However, the Equivalent Series Inductance (ESL) of these

capacitors increases with case size and can reduce the

usefulness of the capacitor to high slew-rate transient loading.

Unfortunately, ESL is not a specified parameter. Work with

your capacitor supplier and measure the capacitor’s

impedance with frequency to select a suitable component. In

most cases, multiple electrolytic capacitors of small case size

perform better than a single large case capacitor.

Output Inductor Selection

The output inductor is selected to meet the output voltage

ripple requirements and minimize the converter’s response

time to the load transient. The inductor value determines the

converter’s ripple current and the ripple voltage is a function

of the ripple current. The ripple voltage and current are

approximated by Equations 12 and 13:

I =

VIN - VOUT

fs x L

x

VOUT

VIN

(EQ. 12)

VOUT = I x ESR

(EQ. 13)

Increasing the value of inductance reduces the ripple current

and voltage. However, the large inductance values reduce

the converter’s response time to a load transient.

One of the parameters limiting the converter’s response to

a load transient is the time required to change the inductor

current. Given a sufficiently fast control loop design, the

ISL6527, ISL6527A will provide either 0% or 100% duty

cycle in response to a load transient. The response time is

the time required to slew the inductor current from an initial

current value to the transient current level. During this

interval the difference between the inductor current and the

transient current level must be supplied by the output

capacitor. Minimizing the response time can minimize the

output capacitance required.

The response time to a transient is different for the application

of load and the removal of load. Equations 14 and 15 give the

11 FN9056.11

September 29, 2015

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet ISL6527A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ISL6527 | Single Synchronous Buck Pulse-Width Modulation (PWM) Controller | Intersil |

| ISL6527A | Single Synchronous Buck Pulse-Width Modulation (PWM) Controller | Intersil |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |