|

|

PDF TMC22153A Data sheet ( Hoja de datos )

| Número de pieza | TMC22153A | |

| Descripción | Multistandard Digital Video Decoder | |

| Fabricantes | Fairchild Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de TMC22153A (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.fairchildsemi.com

TMC22x5yA

Multistandard Digital Video Decoder

Three-Line Adaptive Comb Decoder Family, 8 & 10 bit

Features

• Very high performance, low cost

• Adaptive comb-based decoding

• Multiple pin-compatible versions

- 3-line, 2-line, and band-split

- 8- and 10-bit processing

• Internal digital linestores

• Supports NTSC/PAL field and NTSC frame based

decoding

• Multiple input formats

- CCIR-601/624 (D1), D2, CVBS, YC

• Multiple output formats

- CCIR-601/624 (D1), RGB, YCBCR

• 10-18 Mpps data rate

• Parallel and serial control interface

• Single +5V power supply

Applications

• Studio television equipment

• Personal computer video input

• MPEG and JPEG compression inputs

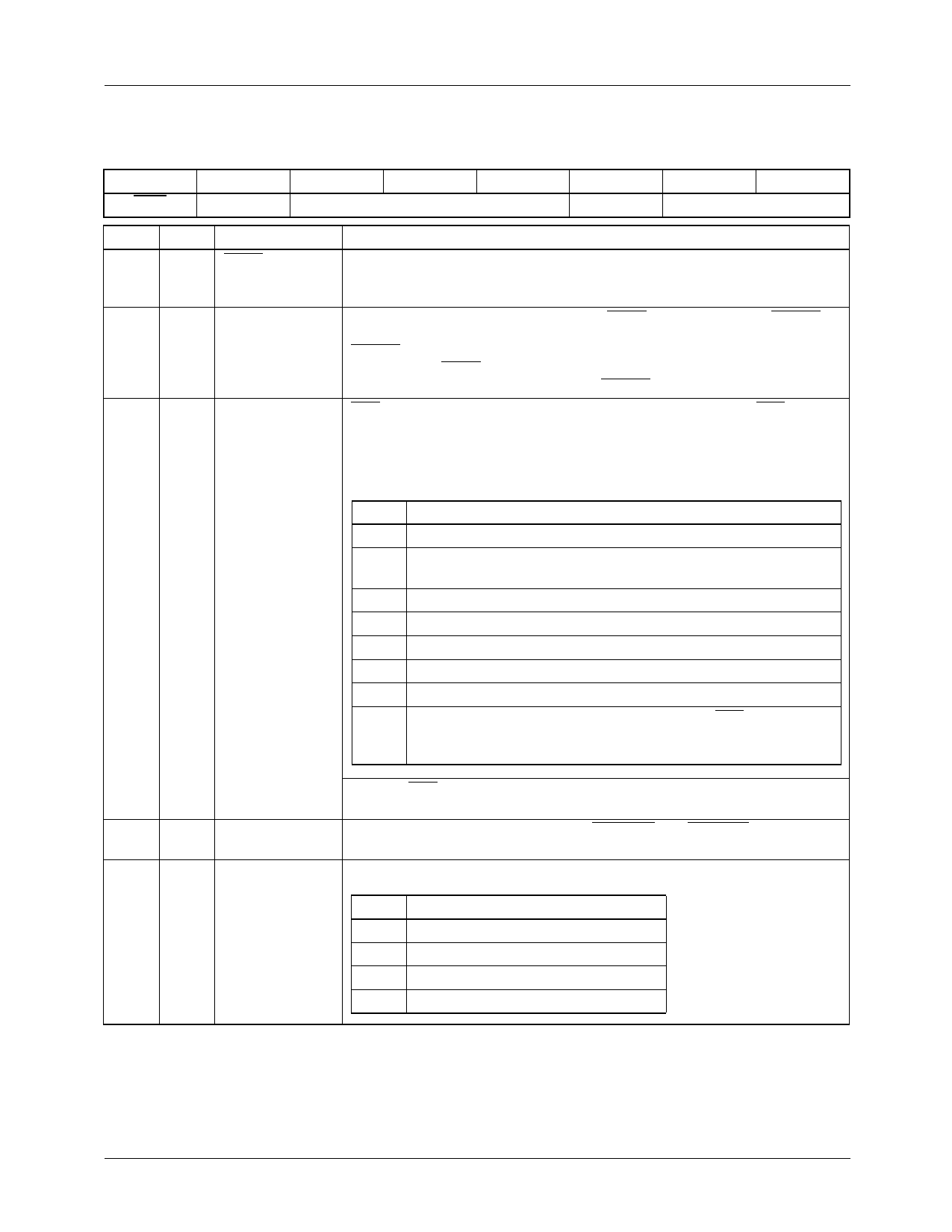

Block Diagram

BUFFER

MASTER1-0

Description

The TMC22x5yA family of Digital Video Decoders offers

unprecedented, broadcast-quality video processing perfor-

mance in a single chip. It accepts line-locked or subcarrier-

locked composite, YC, or D1 digital video and produces dig-

ital components in a variety of formats.

An internal three-line adaptive comb decoder structure pro-

duces optimal picture quality with a wide range of source

material. NTSC/PAL field and NTSC frame based decoding

is supported with external memory. Full comb programma-

bility allows the user to tailor the decoder’s response to a

particular systems goals.

A family of products offers 3-line, 2-line, and simple decod-

ers in 8-bit and 10-bit versions—all in a pin and software-

compatible format. Serial and parallel control ports are pro-

vided. These submicron CMOS devices are packaged in a

100-lead Metric Quad Flat Pack (MQFP).

Related Products

• TMC22071 Genlocking Video Digitizer

• TMC22x9x 8 bit Digital Video Encoders

• TMC2081 Digital Video Mixer

• TMC3003 Triple 10-bit D/A Converter

• TMC1185 10 bit A/D converter

• TMC2192 10 bit video encoder

• TMC2072 Enhanced Genlocking Video Digitizer

VIDEOA9-0

VIDEOB9-0

CLOCK

LDV

HSYNC

VSYNC

Input

Processor

Internal

Sync Pulse

Generator

Linestore1

Linestore2

Y/C Split0

Y/C Split1

Adaptive

Comb

Filter

Y/C Split2

Chroma

Demod

Comb

Fail

Burst

Locked

Loop

Output

Processor

Parallel Control

Global Control

Serial Control

G/Y9-0

B/Cb9-0

R/Cr9-0

FID2-0

DREF

DHSYNC

DVSYNC

A1-0 R/W CS D 7-0 SET RESET SER SA2-0 SDA SCL

65-22x5y-01

Rev. 0.9.0

PRELIMINARY INFORMATION describes products that are not in full production at the time of printing. Specifications are based on design goals

and limited characterization. They may change without notice. Contact Fairchild Semiconductor for current information.

1 page

PRODUCT SPECIFICATION

TMC22x5yA

assumed to be luminance and the high frequency portion is

processed as chrominance to find the magnitude and phase of

the chrominance vector. These three components are then

compared across the (0H & 1H) and (1H & 2H) taps of the

comb filter to produce the difference in luminance, chromi-

nance magnitude, and chrominance phase. These differences

are then translated in the user-programmable lookup table to

produce the “K” signal which controls the complementary

mix between the output of the comb filter and the simple

bandsplit decoder. That is, the “K” signals controls how

much of the combed high frequency luminance signal is sub-

tracted from the simple bandsplit chrominance for chroma

combs, or added to the low frequency output of the bandsplit

for luma comb filters.

Output Processor

The demodulated chrominance signal and the luminance

signal are passed through a programmable output matrix,

producing RGB, YUV, or YCBCR. When the clock is at

27MHz, a D1 signal can be produced on the R/V output with

the embedded TRS words fixed to the external HSYNC and

VSYNC timing.

Parallel and Serial Microprocessor Interfaces

The parallel microprocessor interface employs 12 pins, the

serial port uses 5. A single pin, SER, selects between the two

interface modes.

In parallel interface mode, one address line is decoded for

access to the internal control register and its pointer.

Controls are reached by loading a desired address through

the 8-bit D7-0 port, followed by the desired data (read or

write) for that address. The control register address pointer

auto-increments to address 3Fh and then remains there.

A 2-line serial interface may also be used for initialization

and control. The same set of registers accessed by the paral-

lel port is available to the serial port. The device address in

the serial interface is selected via pins SA2-0.

The RESET pin sets all internal state machines to their ini-

tialized conditions and places the decoder in a power-down

mode. All register data are maintained while in power-down

mode.

Pin Assignments

100

1

81

80

30

31

51

50

65-22x5y-03

Pin Name

1 G/Y1

2 G/Y0

3 LDV

4 GND

5 VDD

6 B/Cb9

7 B/Cb8

8 B/Cb7

9 B/Cb6

10 B/Cb5

11 B/Cb4

12 B/Cb3

13 B/Cb2

14 B/Cb1

15 B/Cb0

16 GND

17 VDD

18 R/Cr9

19 R/Cr8

20 R/Cr7

21 R/Cr6

22 R/Cr5

23 R/Cr4

24 R/Cr3

25 R/Cr2

Pin Name Pin Name

26 R/Cr1 51 RESET

27 R/Cr0 52 SET

28 GND

53 SER

29 VDD

54 SA0

30 DREF 55 SA1

31 FID0

56 SA2

32 FID1

57 GND

33 FID2

58 SDA

34 DHSYNC 59 SCL

35 DVSYNC 60 CS

36 D0

61 R/W

37 D1

62 A0

38 D2

63 A1

39 GND

64 GND

40 VDD

65 VDD

41 D3

66 VIDEOB0

42 D4

67 VIDEOB1

43 D5

68 VIDEOB2

44 D6

69 VIDEOB3

45 D7

70 VIDEOB4

46 GND

71 VIDEOB5

47 VDD

72 VIDEOB6

48 HSYNC 73 VIDEOB7

49 VSYNC 74 VIDEOB8

50 BUFFER 75 VIDEOB9

Pin Name

76 GND

77 VIDEOA0

78 VIDEOA1

79 VIDEOA2

80 VIDEOA3

81 VIDEOA4

82 VIDEOA5

83 VIDEOA6

84 VIDEOA7

85 VIDEOA8

86 VIDEOA9

87 MASTER0

88 MASTER1

89 CLOCK

90 GND

91 VDD

92 GND

93 G/Y9

94 G/Y8

95 G/Y7

96 G/Y6

97 G/Y5

98 G/Y4

99 G/Y3

100 G/Y2

5

5 Page

PRODUCT SPECIFICATION

TMC22x5yA

Control Register Definitions

Global Control Register (00)

76543210

SRST

HRST

SET

DHVEN

STD

Reg Bit

00 7

Name

SRST

00 6

HRST

00 5-3 SET

Description

Software reset. When LOW, resets and holds internal state machines and

disables outputs. When HIGH (normal), starts and runs state machines and

enables outputs. This bit is ignored while HRST is high.

Hardware reset. When HRST is HIGH, SRST is forced low when RESET pin

is taken LOW. State machines are reset and held. When HRST is low the

RESET pin can be taken HIGH at any time. The state machines remain

disabled until SRST is programmed HIGH. When HRST is high the state

machines are enabled as soon as the RESET pin goes HIGH.

SET pin function. These bits control the set function when the SET pin goes

low.

A = all outputs high-impedance

B = internal state machines

C = burst locked loop

SET Function

000 Reset and hold A, B, & C.

001 Set output to BLUE and flywheel B & C. (RGB outputs)

Set output to "color" and flywheel B & C (YCBCR outputs)

010 Hold A, lock B & C to external input

011 Reset C only

100 Reset B & C

101 Set output to BLUE and lock B & C to input video (RGB output)

110 Line and pixel grab depending on VMCR6-0 (reg 30)

111 Toggle reset function of SET = 010. For each SET = 0 pulse the

chip operation will change from normal to that of SET = 010 or

visa versa.

00 2

DHVEN

00 1-0 STD

The first SET pulse after a software or hardware reset, with SET = 111,

causes a toggle to SET = 010.

Output H&V sync enable. Disables DHSYNC and DVSYNC signals when

HIGH.

Selects video standard. Selects video standard.

SET Function

00 NTSC

01 reserved

10 PAL/M

11 All PAL standards except PAL/M

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet TMC22153A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| TMC22153 | Multistandard Digital Video Decoder Three-Line Adaptive Comb Decoder Family/ 8 & 10 bit | Fairchild Semiconductor |

| TMC22153A | Multistandard Digital Video Decoder | Fairchild Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |