|

|

PDF STK11C88 Data sheet ( Hoja de datos )

| Número de pieza | STK11C88 | |

| Descripción | 256 Kbit (32 K x 8) SoftStore nvSRAM | |

| Fabricantes | Cypress Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de STK11C88 (archivo pdf) en la parte inferior de esta página. Total 17 Páginas | ||

|

No Preview Available !

STK11C88

256 Kbit (32 K x 8) SoftStore nvSRAM

Features

■ 25 ns and 45 ns Access Times

■ Pin Compatible with Industry Standard SRAMs

■ Software initiated STORE and RECALL

■ Automatic RECALL to SRAM on Power Up

■ Unlimited Read and Write endurance

■ Unlimited RECALL Cycles

■ 1,000,000 STORE Cycles

■ 100 year Data Retention

■ Single 5 V+10% Power Supply

■ Commercial and Industrial Temperatures

■ 28-pin (300 mil and 330 mil) SOIC packages

■ RoHS compliance

Functional Description

The Cypress STK11C88 is a 256 Kb fast static RAM with a

nonvolatile element in each memory cell. The embedded

nonvolatile elements incorporate QuantumTrap technology

producing the world’s most reliable nonvolatile memory. The

SRAM provides unlimited read and write cycles, while

independent, nonvolatile data resides in the highly reliable

QuantumTrap cell. Data transfers under Software control from

SRAM to the nonvolatile elements (the STORE operation). On

power up, data is automatically restored to the SRAM (the

RECALL operation) from the nonvolatile memory. RECALL

operations are also available under software control.

For a complete list of related documentation, click here.

Logic Block Diagram

Cypress Semiconductor Corporation • 198 Champion Court

Document Number: 001-50591 Rev. *F

• San Jose, CA 95134-1709 • 408-943-2600

Revised March 20, 2015

1 page

STK11C88

Hardware Protect

The STK11C88 offers hardware protection against inadvertent

STORE operation and SRAM WRITEs during low voltage condi-

tions. When VCC<VSWITCH, all externally initiated STORE opera-

tions and SRAM WRITEs are inhibited.

Noise Considerations

The STK11C88 is a high speed memory. It must have a high

frequency bypass capacitor of approximately 0.1 µF connected

between VCC and VSS, using leads and traces that are as short

as possible. As with all high speed CMOS ICs, careful routing of

power, ground, and signals help prevent noise problems.

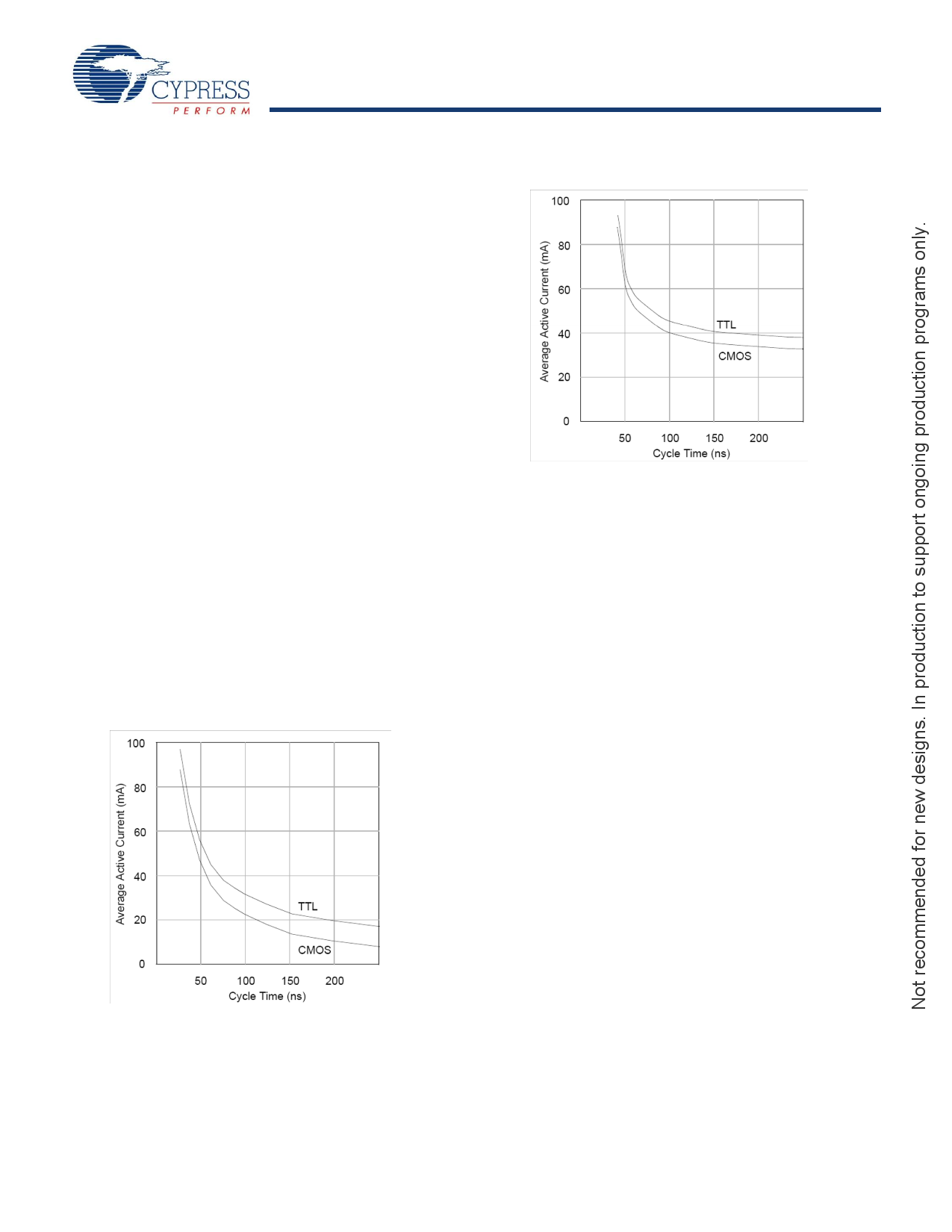

Low Average Active Power

CMOS technology provides the STK11C88 the benefit of

drawing significantly less current when it is cycled at times longer

than 50 ns. Figure 2 and Figure 3 show the relationship between

ICC and READ or WRITE cycle time. Worst case current

consumption is shown for both CMOS and TTL input levels

(commercial temperature range, VCC = 5.5V, 100 percent duty

cycle on chip enable). Only standby current is drawn when the

chip is disabled. The overall average current drawn by the

STK11C88 depends on the following items:

1. The duty cycle of chip enable

2. The overall cycle rate for accesses

3. The ratio of READs to WRITEs

4. CMOS versus TTL input levels

5. The operating temperature

6. The VCC level

7. I/O loading

Figure 2. Icc (max) Reads

Figure 3. Icc (max) Writes

Best Practices

nvSRAM products have been used effectively for over 15 years.

While ease-of-use is one of the product’s main system values,

the experience gained working with hundreds of applications has

resulted in the following suggestions as best practices:

■ The nonvolatile cells in a nvSRAM are programmed on the test

floor during final test and quality assurance. Incoming

inspection routines at customer or contract manufacturer’s

sites, sometimes, reprogram these values. Final NV patterns

are typically repeating patterns of AA, 55, 00, FF, A5, or 5A.

The end product’s firmware should not assume that a NV array

is in a set programmed state. Routines that check memory

content values to determine first time system configuration and

cold or warm boot status, should always program a unique NV

pattern (for example, a complex 4-byte pattern of 46 E6 49 53

hex or more random bytes) as part of the final system manufac-

turing test to ensure these system routines work consistently.

■ Power up boot firmware routines should rewrite the nvSRAM

into the desired state. While the nvSRAM is shipped in a preset

state, best practice is to again rewrite the nvSRAM into the

desired state as a safeguard against events that might flip the

bit inadvertently (program bugs or incoming inspection

routines).

Document Number: 001-50591 Rev. *F

Page 5 of 17

5 Page

STK11C88

STORE INHIBIT or Power Up RECALL

Parameter

Alt

tHRECALL [10]

tSTORE [6]

VRESET

VSWITCH

tRESTORE

tHLHZ

Switching Waveforms

Description

Power up RECALL Duration

STORE Cycle Duration

Low Voltage Reset Level

Low Voltage Trigger Level

Figure 9. STORE INHIBIT/Power Up RECALL

STK11C88

Min Max

550

10

3.6

4.0 4.5

VCC

5V

VSWITCH

VRESET

Unit

s

ms

V

V

STORE INHIBIT

POWER-UP RECALL

DQ (DATA OUT)

tHRECALL

POWER-UP

RECALL

BROWN OUT

STORE INHIBIT

NO RECALL

(VCC DID NOT GO

BELOW VRESET)

BROWN OUT

STORE INHIBIT

NO RECALL

(VCC DID NOT GO

BELOW VRESET)

BROWN OUT

STORE INHIBIT

RECALL WHEN

VCC RETURNS

ABOVE VSWITCH

Note

10. tHRECALL starts from the time VCC rises above VSWITCH.

Document Number: 001-50591 Rev. *F

Page 11 of 17

11 Page | ||

| Páginas | Total 17 Páginas | |

| PDF Descargar | [ Datasheet STK11C88.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| STK11C88 | 256 Kbit (32 K x 8) SoftStore nvSRAM | Cypress Semiconductor |

| STK11C88 | 32Kx8 SoftStore nvSRAM | Simtek |

| STK11C88-3 | 32K X 8 NVSRAM 3.3 V QUANTUM TRAP CMOS NONVOLATILE STATIC RAM | Simtek |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |