|

|

PDF CY62126ESL Data sheet ( Hoja de datos )

| Número de pieza | CY62126ESL | |

| Descripción | 1-Mbit (64 K x 16) Static RAM | |

| Fabricantes | Cypress Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de CY62126ESL (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

CY62126ESL MoBL®

1-Mbit (64 K × 16) Static RAM

1-Mbit (64 K × 16) Static RAM

Features

■ Very high speed: 45 ns

■ Wide voltage range: 2.2 V to 3.6 V and 4.5 V to 5.5 V

■ Ultra low standby power

❐ Typical standby current: 1 A

❐ Maximum standby current: 4 A

■ Ultra low active power

❐ Typical active current: 1.3 mA at f = 1 MHz

■ Easy memory expansion with CE, and OE features

■ Automatic power down when deselected

■ Complementary metal oxide semiconductor (CMOS) for

optimum speed and power

■ Available in Pb-free 44-pin thin small outline package (TSOP)

Type II package

Functional Description

The CY62126ESL is a high performance CMOS static RAM

organized as 64K words by 16 bits. This device features

advanced circuit design to provide ultra low active current. This

is ideal for providing More Battery Life™ (MoBL) in portable

applications. The device also has an automatic power down

feature that significantly reduces power consumption when

addresses are not toggling. Placing the device into standby

mode reduces power consumption by more than 99 percent

when deselected (CE HIGH). The input and output pins (I/O0

through I/O15) are placed in a high impedance state when the

device is deselected (CE HIGH), the outputs are disabled (OE

HIGH), both Byte High Enable and Byte Low Enable are disabled

(BHE, BLE HIGH) or during a write operation (CE LOW and WE

LOW).

To write to the device, take Chip Enable (CE) and Write Enable

(WE) inputs LOW. If Byte Low Enable (BLE) is LOW, then data

from I/O pins (I/O0 through I/O7) is written into the location

specified on the address pins (A0 through A15). If Byte High

Enable (BHE) is LOW, then data from I/O pins (I/O8 through

I/O15) is written into the location specified on the address pins

(A0 through A15).

To read from the device, take Chip Enable (CE) and Output

Enable (OE) LOW while forcing the Write Enable (WE) HIGH. If

Byte Low Enable (BLE) is LOW, then data from the memory

location specified by the address pins appear on I/O0 to I/O7. If

Byte High Enable (BHE) is LOW, then data from memory

appears on I/O8 to I/O15. See the Truth Table on page 11 for a

complete description of read and write modes.

The CY62126ESL device is suitable for interfacing with

processors that have TTL I/P levels. It is not suitable for

processors that require CMOS I/P levels. Please see Electrical

Characteristics on page 4 for more details and suggested

alternatives.

For a complete list of related resources, click here.

Logic Block Diagram

DATA IN DRIVERS

A10

A9

A8

A7

AA65

A4

64 K × 16

RAM Array

A3

A2

A1

A0

I/O0–I/O7

I/O8–I/O15

COLUMN DECODER

BHE

WE

CE

OE

BLE

Cypress Semiconductor Corporation • 198 Champion Court

Document Number: 001-45076 Rev. *I

• San Jose, CA 95134-1709 • 408-943-2600

Revised December 10, 2014

1 page

CY62126ESL MoBL®

Capacitance

Parameter [10]

Description

CIN

COUT

Input capacitance

Output capacitance

Thermal Resistance

Parameter [10]

Description

JA Thermal resistance

(junction to ambient)

JC Thermal resistance

(junction to case)

Test Conditions

TA = 25 °C, f = 1 MHz, VCC = VCC(typ)

Max Unit

10 pF

10 pF

Test Conditions

44-pin TSOP II Unit

Still air, soldered on a 3 × 4.5 inch, two-layer printed circuit 28.2 C/W

board

3.4 C/W

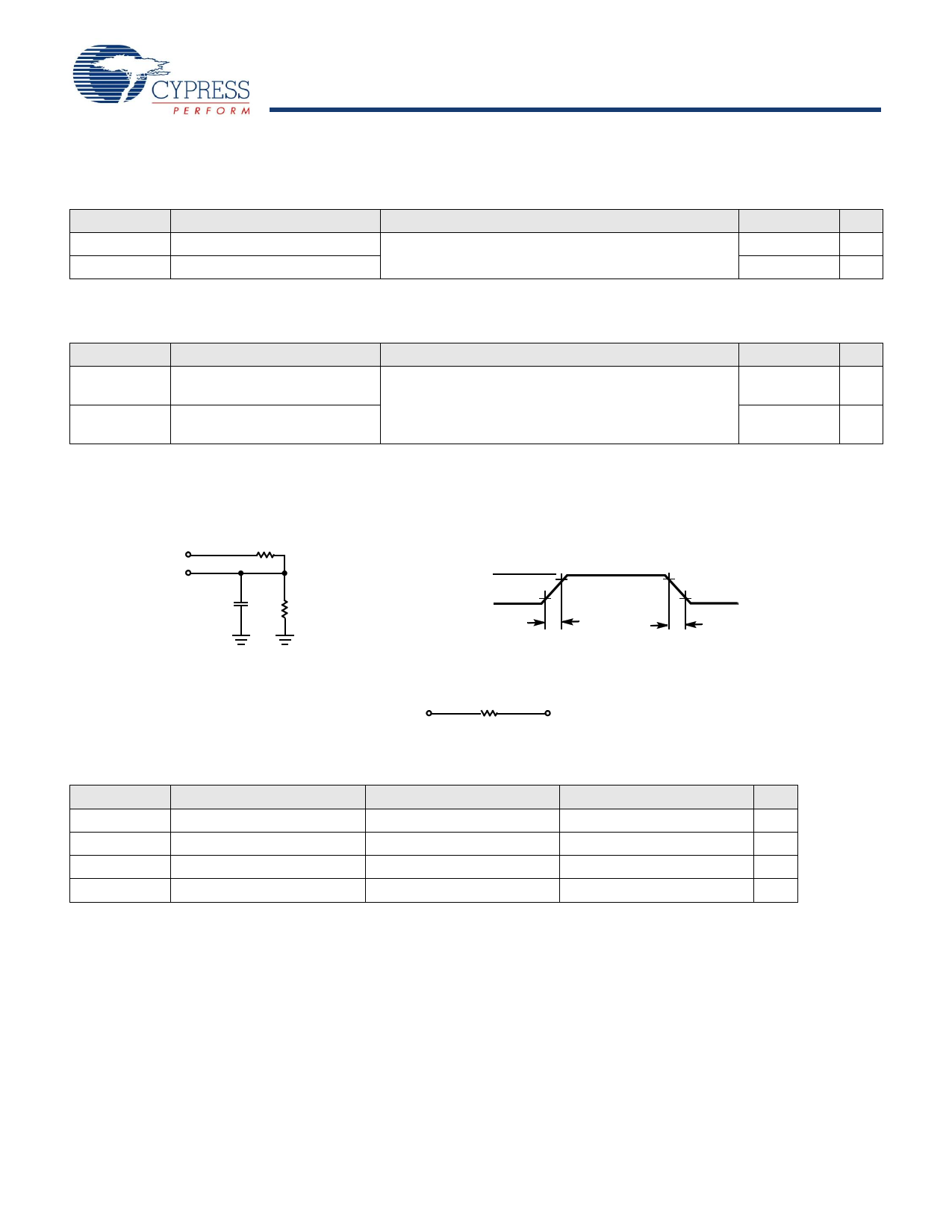

AC Test Loads and Waveforms

Figure 1. AC Test Loads and Waveforms

VCC

OUTPUT

R1

30 pF

R2

ALL INPUT PULSES

VCC

10%

GND

Rise Time = 1 V/ns

90%

90%

10%

Fall Time = 1 V/ns

INCLUDING

JIG AND

SCOPE

Equivalent to: THEVENIN EQUIVALENT

OUTPUT

RTH

V

Parameters

R1

R2

RTH

VTH

2.50 V

16600

15400

8000

1.2

3.0 V

1103

1554

645

1.75

5.0 V

1800

990

639

1.77

Unit

V

Note

10. Tested initially and after any design or process changes that may affect these parameters.

Document Number: 001-45076 Rev. *I

Page 5 of 16

5 Page

CY62126ESL MoBL®

Truth Table

CE [27] WE

HX

LX

LH

LH

OE

X

X

L

L

LHL

L HH

L HH

L HH

LLX

LLX

LLX

BHE

X

H

L

H

L

L

H

L

L

H

L

BLE

X

H

L

L

H

L

L

H

L

L

H

Inputs/Outputs

High Z

High Z

Data out (I/O0–I/O15)

Data out (I/O0–I/O7);

I/O8–I/O15 in High Z

Data Out (I/O8–I/O15);

I/O0–I/O7 in High Z

High Z

High Z

High Z

Data in (I/O0–I/O15)

Data in (I/O0–I/O7);

I/O8–I/O15 in High Z

Data in (I/O8–I/O15);

I/O0–I/O7 in High Z

Mode

Deselect or power down

Output disabled

Read

Read

Read

Output disabled

Output disabled

Output disabled

Write

Write

Write

Power

Standby (ISB)

Active (ICC)

Active (ICC)

Active (ICC)

Active (ICC)

Active (ICC)

Active (ICC)

Active (ICC)

Active (ICC)

Active (ICC)

Active (ICC)

Note

27. Chip enable must be at CMOS levels (not floating). Intermediate voltage levels on this pin is not permitted.

Document Number: 001-45076 Rev. *I

Page 11 of 16

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet CY62126ESL.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CY62126ESL | 1-Mbit (64 K x 16) Static RAM | Cypress Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |