|

|

PDF CY7C1562XV18 Data sheet ( Hoja de datos )

| Número de pieza | CY7C1562XV18 | |

| Descripción | 72-Mbit QDR II+ Xtreme SRAM Two-Word Burst Architecture | |

| Fabricantes | Cypress Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de CY7C1562XV18 (archivo pdf) en la parte inferior de esta página. Total 29 Páginas | ||

|

No Preview Available !

CY7C1562XV18/CY7C1564XV18

72-Mbit QDR® II+ Xtreme SRAM Two-Word

Burst Architecture (2.5 Cycle Read Latency)

72-Mbit QDR® II+ Xtreme SRAM Two-Word Burst Architecture (2.5 Cycle Read Latency)

Features

■ Separate independent read and write data ports

❐ Supports concurrent transactions

■ 450 MHz clock for high bandwidth

■ Two-word burst for reducing address bus frequency

■ Double Data Rate (DDR) interfaces on both read and write ports

(data transferred at 900 MHz) at 450 MHz

■ Available in 2.5 clock cycle latency

■ Two input clocks (K and K) for precise DDR timing

❐ SRAM uses rising edges only

■ Echo clocks (CQ and CQ) simplify data capture in high speed

systems

■ Data valid pin (QVLD) to indicate valid data on the output

■ Single multiplexed address input bus latches address inputs

for both read and write ports

■ Separate port selects for depth expansion

■ Synchronous internally self-timed writes

■ QDR™-II+ Xtreme operates with 2.5 cycle read latency when

DOFF is asserted HIGH

■ Operates similar to QDR-I device with 1 cycle read latency

when DOFF is asserted LOW

■ Available in × 18, and × 36 configurations

■ Full data coherency, providing most current data

■ Core VDD = 1.8 V± 0.1 V; I/Os VDDQ = 1.4 V to 1.6 V

❐ Supports 1.5 V I/O supply

■ HSTL inputs and variable drive HSTL output buffers

■ Available in 165-ball FBGA package (13 × 15 × 1.4 mm)

■ Offered in both Pb-free and non Pb-free packages

■ JTAG 1149.1 compatible test access port

■ Phase-Locked Loop (PLL) for accurate data placement

Configurations

With Read Cycle Latency of 2.5 cycles:

CY7C1562XV18 – 4M × 18

CY7C1564XV18 – 2M × 36

Functional Description

The CY7C1562XV18, and CY7C1564XV18 are 1.8 V

Synchronous Pipelined SRAMs, equipped with QDR® II+

architecture. Similar to QDR II architecture, QDR II+ architecture

consists of two separate ports: the read port and the write port to

access the memory array. The read port has dedicated data

outputs to support read operations and the write port has

dedicated data inputs to support write operations. QDR II+

architecture has separate data inputs and data outputs to

completely eliminate the need to “turnaround” the data bus that

exists with common I/Os devices. Access to each port is through

a common address bus. Addresses for read and write addresses

are latched on alternate rising edges of the input (K) clock.

Accesses to the QDR II+ Xtreme read and write ports are

completely independent of one another. To maximize data

throughput, both read and write ports are equipped with DDR

interfaces. Each address location is associated with two 18-bit

words (CY7C1562XV18), or 36-bit words (CY7C1564XV18) that

burst sequentially into or out of the device. Because data can be

transferred into and out of the device on every rising edge of both

input clocks (K and K), memory bandwidth is maximized while

simplifying system design by eliminating bus “turnarounds”.

Depth expansion is accomplished with port selects, which

enables each port to operate independently.

All synchronous inputs pass through input registers controlled by

the K or K input clocks. All data outputs pass through output

registers controlled by the K or K input clocks. Writes are

conducted with on-chip synchronous self-timed write circuitry.

For a complete list of related documentation, click here.

Selection Guide

Maximum Operating Frequency

Maximum Operating Current

Description

450 MHz 366 MHz Unit

450 366 MHz

× 18 1205

970 mA

× 36 1445

1165

Cypress Semiconductor Corporation • 198 Champion Court

Document Number: 001-68998 Rev. *F

• San Jose, CA 95134-1709 • 408-943-2600

Revised July 7, 2016

1 page

CY7C1562XV18/CY7C1564XV18

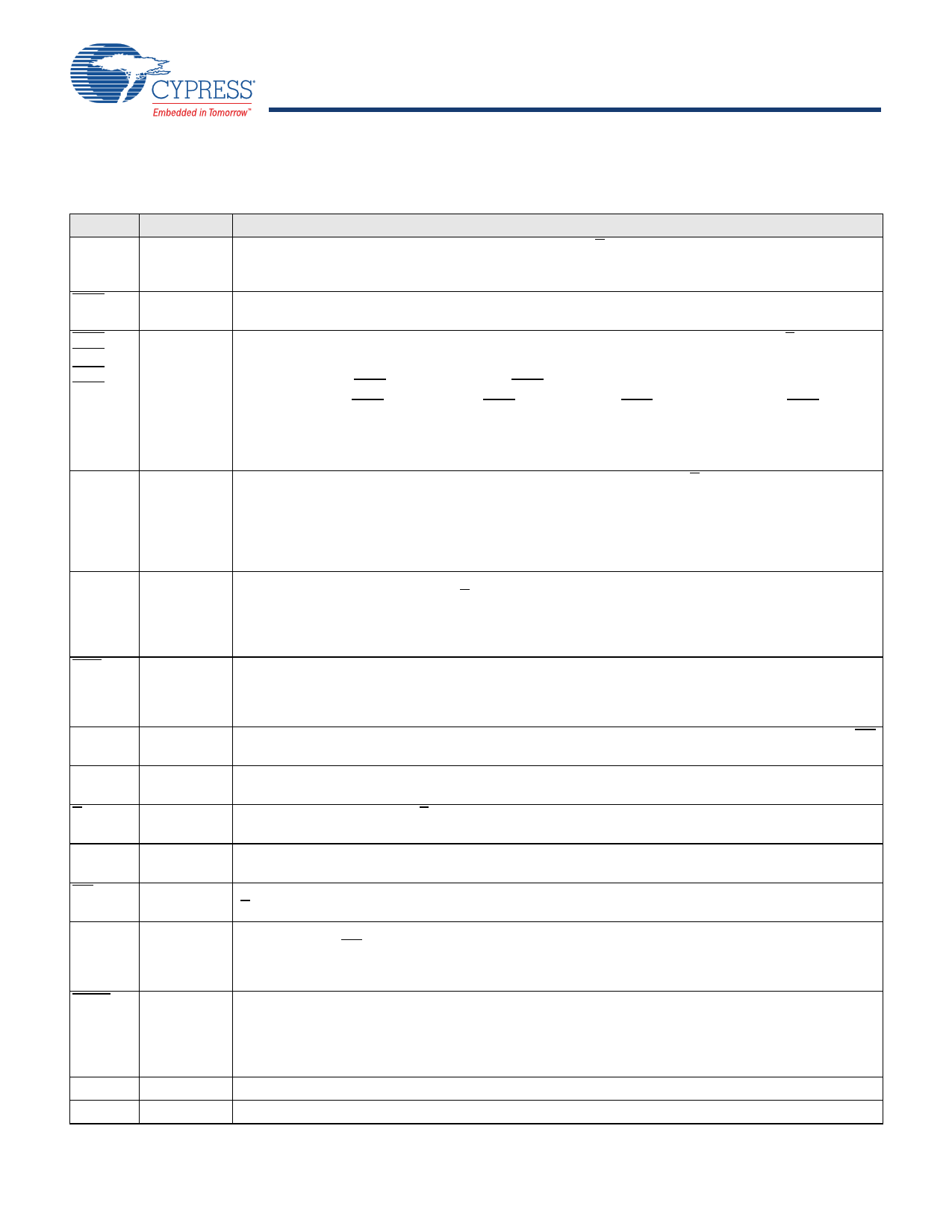

Pin Definitions

Pin Name

I/Os

Pin Description

D[x:0]

WPS

BWS0,

BWS1,

BWS2,

BWS3

Input- Data Input Signals. Sampled on the rising edge of K and K clocks during valid write operations.

Synchronous CY7C1562XV18 D[17:0]

CY7C1564XV18 D[35:0]

Input- Write Port Select Active LOW. Sampled on the rising edge of the K clock. When asserted active, a

Synchronous write operation is initiated. Deasserting deselects the write port. Deselecting the write port ignores D[x:0].

Input- Byte Write Select 0, 1, 2 and 3 Active LOW. Sampled on the rising edge of the K and K clocks during

Synchronous write operations. Used to select which byte is written into the device during the current portion of the write

operations. Bytes not written remain unaltered.

CY7C1562XV18 BWS0 controls D[8:0] and BWS1 controls D[17:9].

CY7C1564XV18 BWS0 controls D[8:0], BWS1 controls D[17:9], BWS2 controls D[26:18] and BWS3 controls

D[35:27].

All the Byte Write Selects are sampled on the same edge as the data. Deselecting a Byte Write Select

ignores the corresponding byte of data and it is not written into the device.

A Input- Address Inputs. Sampled on the rising edge of the K (read address) and K (write address) clocks during

Synchronous active read and write operations. These address inputs are multiplexed for both read and write operations.

Internally, the device is organized as 4M × 18 (2 arrays each of 2M × 18) for CY7C1562XV18, and 2M × 36

(2 arrays each of 1M × 36) for CY7C1564XV18. Therefore, only 21 address inputs for CY7C1562XV18,

and 20 address inputs for CY7C1564XV18. These inputs are ignored when the appropriate port is

deselected. The address pins (A) can be assigned any bit order.

Q[x:0]

RPS

Output- Data Output Signals. These pins drive out the requested data during a read operation. Valid data is driven

Synchronous out on the rising edge of the K and K clocks during read operations. When the read port is deselected,

Q[x:0] are automatically tristated.

CY7C1562XV18 Q[17:0]

CY7C1564XV18 Q[35:0]

Input- Read Port Select Active LOW. Sampled on the rising edge of positive input clock (K). When active, a

Synchronous read operation is initiated. Deasserting deselects the read port. When deselected, the pending access is

allowed to complete and the output drivers are automatically tristated following the next rising edge of the

K clock. Each read access consists of a burst of two sequential transfers.

QVLD

Valid output Valid Output Indicator. The Q Valid indicates valid output data. QVLD is edge aligned with CQ and CQ.

indicator

K Input Clock Positive Input Clock Input. The rising edge of K is used to capture synchronous inputs to the device and

to drive out data through Q[x:0]. All accesses are initiated on the rising edge of K.

K Input Clock Negative Input Clock Input. K is used to capture synchronous inputs being presented to the device and

to drive out data through Q[x:0].

CQ Echo Clock Synchronous Echo Clock Outputs. This is a free running clock and is synchronized to the input clock

(K) of the QDR II+ Xtreme. The timing for the echo clocks is shown in Switching Characteristics on page 23.

CQ Echo Clock Synchronous Echo Clock Outputs. This is a free running clock and is synchronized to the input clock

(K) of the QDR II+ Xtreme. The timing for the echo clocks is shown in Switching Characteristics on page 23.

ZQ Input Output Impedance Matching Input. This input is used to tune the device outputs to the system data bus

impedance. CQ, CQ, and Q[x:0] output impedance are set to 0.2 × RQ, where RQ is a resistor connected

between ZQ and ground. Alternatively, connect this pin directly to VDDQ, which enables the minimum

impedance mode. This pin cannot be connected directly to GND or left unconnected.

DOFF

Input

PLL Turn Off Active LOW. Connecting this pin to ground turns off the PLL inside the device. The timing

in the operation with the PLL turned off differs from those listed in this data sheet. For normal operation,

connect this pin to a pull up through a 10 K or less pull up resistor. The device behaves in QDR-I mode

when the PLL is turned off. In this mode, the device can be operated at a frequency of up to 167 MHz with

QDR-I timing.

TDO

Output TDO Pin for JTAG

TCK

Input TCK Pin for JTAG

Document Number: 001-68998 Rev. *F

Page 5 of 29

5 Page

CY7C1562XV18/CY7C1564XV18

IEEE 1149.1 Serial Boundary Scan (JTAG)

These SRAMs incorporate a serial boundary scan Test Access

Port (TAP) in the FBGA package. This part is fully compliant with

IEEE Standard #1149.1-2001. The TAP operates using JEDEC

standard 1.8 V I/Os logic levels.

Disabling the JTAG Feature

It is possible to operate the SRAM without using the JTAG

feature. To disable the TAP controller, TCK must be tied LOW

(VSS) to prevent clocking of the device. TDI and TMS are

internally pulled up and may be unconnected. They may

alternatively be connected to VDD through a pull up resistor. TDO

must be left unconnected. Upon power up, the device comes up

in a reset state, which does not interfere with the operation of the

device.

Test Access Port

Test Clock

The test clock is used only with the TAP controller. All inputs are

captured on the rising edge of TCK. All outputs are driven from

the falling edge of TCK.

Test Mode Select (TMS)

The TMS input is used to give commands to the TAP controller

and is sampled on the rising edge of TCK. This pin may be left

unconnected if the TAP is not used. The pin is pulled up

internally, resulting in a logic HIGH level.

Test Data-In (TDI)

The TDI pin is used to serially input information into the registers

and can be connected to the input of any of the registers. The

register between TDI and TDO is chosen by the instruction that

is loaded into the TAP instruction register. For information on

loading the instruction register, see TAP Controller State

Diagram on page 13. TDI is internally pulled up and can be

unconnected if the TAP is unused in an application. TDI is

connected to the most significant bit (MSB) on any register.

Test Data-Out (TDO)

The TDO output pin is used to serially clock data out from the

registers. The output is active, depending upon the current state

of the TAP state machine (see Instruction Codes on page 17).

The output changes on the falling edge of TCK. TDO is

connected to the least significant bit (LSB) of any register.

Performing a TAP Reset

A Reset is performed by forcing TMS HIGH (VDD) for five rising

edges of TCK. This Reset does not affect the operation of the

SRAM and can be performed while the SRAM is operating. At

power up, the TAP is reset internally to ensure that TDO comes

up in a high Z state.

TAP Registers

Registers are connected between the TDI and TDO pins to scan

the data in and out of the SRAM test circuitry. Only one register

can be selected at a time through the instruction registers. Data

is serially loaded into the TDI pin on the rising edge of TCK. Data

is output on the TDO pin on the falling edge of TCK.

Instruction Register

Three-bit instructions can be serially loaded into the instruction

register. This register is loaded when it is placed between the TDI

and TDO pins, as shown in TAP Controller Block Diagram on

page 14. Upon power up, the instruction register is loaded with

the IDCODE instruction. It is also loaded with the IDCODE

instruction if the controller is placed in a reset state, as described

in the previous section.

When the TAP controller is in the Capture-IR state, the two least

significant bits are loaded with a binary “01” pattern to allow for

fault isolation of the board level serial test path.

Bypass Register

To save time when serially shifting data through registers, it is

sometimes advantageous to skip certain chips. The bypass

register is a single-bit register that can be placed between TDI

and TDO pins. This enables shifting of data through the SRAM

with minimal delay. The bypass register is set LOW (VSS) when

the BYPASS instruction is executed.

Boundary Scan Register

The boundary scan register is connected to all of the input and

output pins on the SRAM. Several No Connect (NC) pins are also

included in the scan register to reserve pins for higher density

devices.

The boundary scan register is loaded with the contents of the

RAM input and output ring when the TAP controller is in the

Capture-DR state and is then placed between the TDI and TDO

pins when the controller is moved to the Shift-DR state. The

EXTEST, SAMPLE/PRELOAD, and SAMPLE Z instructions can

be used to capture the contents of the input and output ring.

The section Boundary Scan Order on page 18 shows the order

in which the bits are connected. Each bit corresponds to one of

the bumps on the SRAM package. The MSB of the register is

connected to TDI, and the LSB is connected to TDO.

Identification (ID) Register

The ID register is loaded with a vendor-specific, 32-bit code

during the Capture-DR state when the IDCODE command is

loaded in the instruction register. The IDCODE is hardwired into

the SRAM and can be shifted out when the TAP controller is in

the Shift-DR state. The ID register has a vendor code and other

information described in Identification Register Definitions on

page 17.

TAP Instruction Set

Eight different instructions are possible with the three-bit

instruction register. All combinations are listed in Instruction

Codes on page 17. Three of these instructions are listed as

RESERVED and must not be used. The other five instructions

are described in this section in detail.

Instructions are loaded into the TAP controller during the Shift-IR

state when the instruction register is placed between TDI and

TDO. During this state, instructions are shifted through the

instruction register through the TDI and TDO pins. To execute

the instruction after it is shifted in, the TAP controller must be

moved into the Update-IR state.

Document Number: 001-68998 Rev. *F

Page 11 of 29

11 Page | ||

| Páginas | Total 29 Páginas | |

| PDF Descargar | [ Datasheet CY7C1562XV18.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CY7C1562XV18 | 72-Mbit QDR II+ Xtreme SRAM Two-Word Burst Architecture | Cypress Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |