|

|

PDF UPD780 Data sheet ( Hoja de datos )

| Número de pieza | UPD780 | |

| Descripción | 8-BIT N-CHANNEL MICROPROCESSOR | |

| Fabricantes | NEC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de UPD780 (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

NEe Microcomputers, Inc.

NEe

J.L PD780

J.L PD780·1

8·BIT N·CHANNEL MICROPROCESSOR

COMPLETELY Z80™ COMPATIBLE

DESC RIPTI ON

The pPD780 and pPD780-1 processors are single-chip microprocessors developed from

third-generation technology,Their increased computational power produces higher

system through-put and more efficient memory utilization, surpassing that of any

second-generation microprocessor, The single voltage requirement of the t1PD780 and

IlPD780-1 processors makes it easy to implement them into a system. All output sig-

nals are fully decoded and timed to either standard memory or peripheral circuits. An

N-channel, ion-implanted, silicon gate MOS process is utilized in implementing the

circuit.

The block diagram shows the functions of the processor and details the internal register

structure. The structure contains 26 bytes of Read/Write (R/W) memory available to

the programmer. Included in the registers are two sets of six general purpose registers,

which may be used individually as S-bit registers, or as 6-bit register pairs. Also

included are two sets of accumulator and flag registers.

Through a group of exchange instructions the programmer has access to either set of

main or alternate registers. The alternate register permits foreground/background mode

of operation, or may be u~ed fv( fast interrupt response. A l6-bit stack pointer is also

included in each processor, simplifying implementation of multiple level interrupts,

permitting unlimited subroutine nesting, and simplifying many types of data handling.

The two 16-bit index registers simplify implementation of relocatable code and manipu-

lation of tabular data. The refresh register automatically refreshes external dynamic

memories. A powerful interrupt response mode uses the I register to form the

upper 8 bits of a pointer to an interrupt service address table, while the interrupting

apparatus supplies the lower 8 bits of the pointer. An indirect call will then be made to

service this address.

FEATU RES

• Single Chip, N-Channel Silicon Gate Processor

• 158 Instructions - Including all 78 of the 8080A Instructions, Permitting Total

Software Compatibility

• New 4-,8-, and 16-8it Operations Featuring Useful Addressing Modes such as

Indexed, Bit and Relative

• 17 Interndl Registers

• Three Modes of Rapid Interrupt Response, and One Non-Maskable Interrupt

• Directly Connects Standard Speed Dynamic or Static Memories, with Minimum

Support Circuitry

• Single-Phase +5 Volt Clock and 5 VDC Supply

• TTL Compatibility

• Automatic Dynamic RAM Refresh Circuitry

• Available in Plastic Package

PIN CONFIGURATION

A11

A'2

A13

A'4

A'5

¢

D4

D3

D5

D6

+5V

02

D7

00

0,

INT

NMI

HALT

MREO

IORO

4

5

6

10

11

12

13

14

15

16

17

18

pPD

780/

780-1

A10

39 A9

38 A8

37 A7

:36 A6

35 A5

34 A4

33 A3

32 A2

31 A,

30 AO

29 GNO

28 RFSH

27 M,

26 RESET

25 BUSRO

24 WAIT

23 BUSAK

22 WR

21 AD

II

TM:Z80 is a registered trademark of Zilog, Inc_

367-

1 page

JLPD780

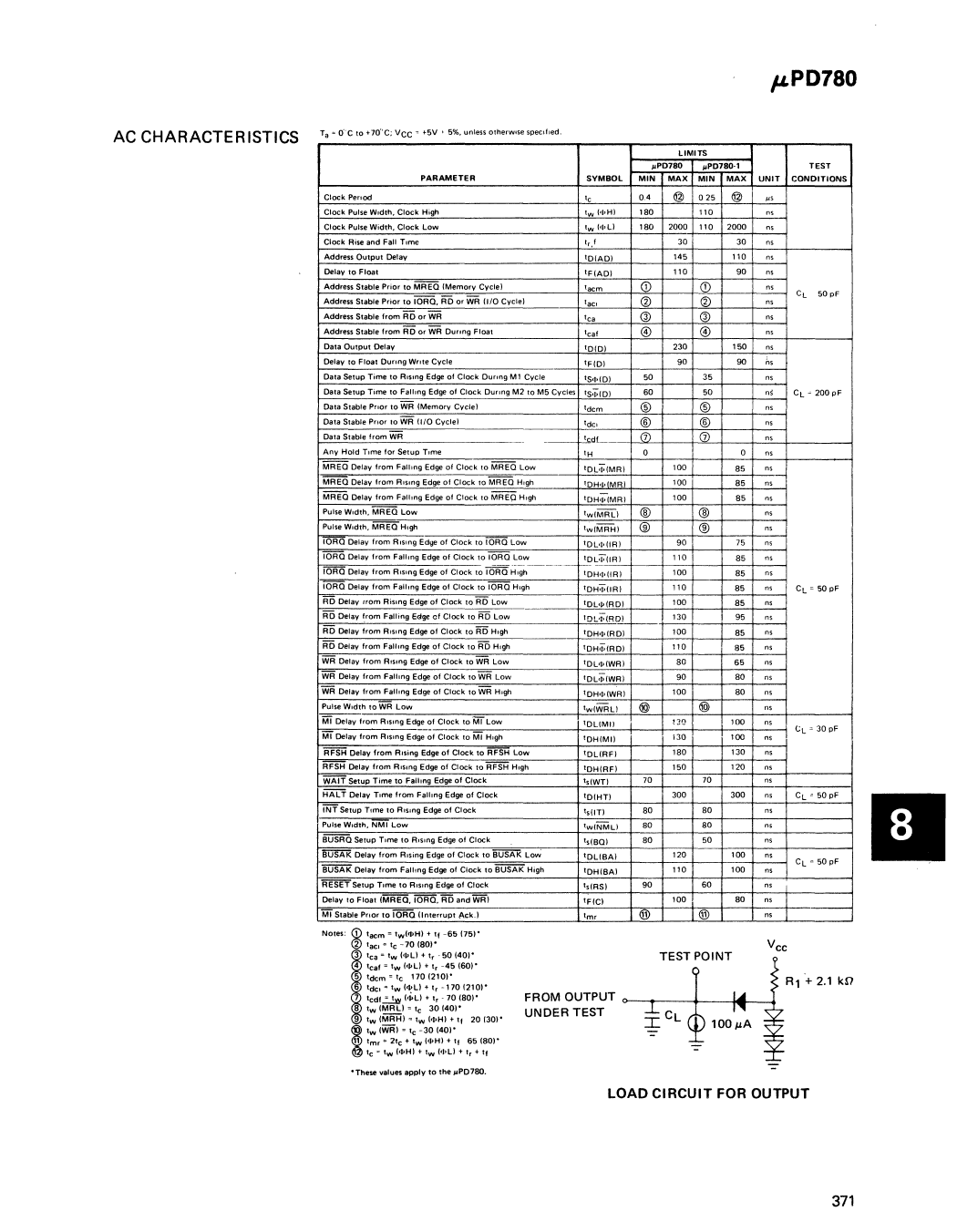

AC CHARACTERISTICS

Ta = o"c to +70"C; Vee ~ +5V ' 5%, unless otherWise speCified.

PARAMETER

SYMBOL

LIMITS

,uPD780 ,uPD780·1

MIN MAX MIN MAX

UNIT

TEST

CONDITIONS

Clock Period

Clock Pulse Width, Clock High

'e

tw ('j,HI

04 @ 025 @

180 110

Clock Pulse Width, Clock Low

twl'i'U

180 2000 110 2000

Clock Rise and Fall Time

Ir ,! 30 30

Address Output Delay

'D(AD)

145 110

Delay to Float

Address Stable Prior to MREQ (Memory Cycle)

Address Stable Prior to IORO, RD or WA (110 Cycle)

Address Siable from AD or WR

Address Siable from AD or WR Dunng Float

IF (AD)

'oem

'aci

'"

teaf

110

Q)

@0

@@

®®

90

Data Output Delay

Delay to Float Dunng Write Cycle

'DID)

'FlO)

230 150

90 90

Data Setup Time to RISing Edge of Clock DUring Ml Cycle

IS'HO)

Data Setup Time 10 Falling Edge of Clock DUring M2 to M5 Cycles Is·pm)

Dala Slable Pnor 10 WR !Memory Cycle)

'0Dala Slable Prior WR UfO Cycle)

Idcm

Idcl

Dala Slable from WR

Any Hold Time for Setup Time

- - .!'&'df

'H

MREQ Delay from Failing Edge of Clock to MREQ Low

IOL'I'(MR)

50

60

®

®

35

50

®

®

(j)

100

"'

85

MREO Delay from RIsing Edge of Clock to MREO High

IOH,t, MR

100 85

MREO Delay hom FaHlng Edge of Clock to MREP High

Pulse Width, MREO Low

Pulse Width, MREO High

10RO Delay from RIsing Ed\:le of Clock to 10RO low

'OH",(MR)

'wIMRLl

tw(MRH)

tOU·IIA)

®

®

100

®

®

90

85

75

10AG Delay from Failing Edge of Clock to 10RO low

10AG Delay from RIsing Edge of Clock to lORa High

t-.- .. tDL,Io(IAI

tDH'io(fAI

110 85

100 85

lORa Delay from FaHlng Edge of Clock to 10RG High

tOH't_(lAl

110 85

AD Delay from RiSing Edge of Clock 10 AD low

RO Delay from Falling Edge of Clock 10 AD Low

AD Delay hom RIsing Edge of Clock 10 AD High

AD Delay from Failing Edge of Clock 10 RD High

'Ol"dRO) 100 85

IDl'HRDI 130 95

tDH'lo/RD) 100 85

IOH'I,(RD) 110 85

WR Delay from RIsing Edge of Clock to WR low

IDl'l-dWRl

80 65

WR Delay from Failing Edge of Clock 10 WR Low

IOL'I>IWR)

90 80

WR Delay from Failing Edge of Clock to WA High

Pulse Width to WA Low

MI Delay from RIsing Edge 01 Clock 10 MI Low

IDH'I·!WRl

Iw(WALl

'DL(MJ)

@

100

@>

DQ

80

100

MI Delay from Rls.ng Edge of Clock to MI High

'DH(MI)

130 100

RFSH Delay from Rising Edge of Clock to AFSH low

tDL(RF)

180 130

RFSH Delay from RIsing Edge of Clock 10 RFSH High

WAIT Setup Time to Failing Edge of Clock

'OH(RF)

Is(WTl

150 120

70 70

HALT Delay Time from Failing Edge of Clock

to(HT)

300 300

INT Setup Time 10 RIsing Edge 01 Clock

Pulse Width, NMI Low

'sIlT)

'wINML)

80

80

80

80

BUSRO Selup Time to R,slng Edge of Clock

Is(BO)

80

50

8USAK Delay hom Rising Edge of Clock to BUSAK low

'OL(BA)

120 100

BUSAK Delay from Failing Edge of Clock to BUSAK High

tDH(BA)

110 100

RESET Setup Time to R'slng Edge of Clock

's(AS}

90

60

Delay 10 Floal (MREQ, IORG. RD and WR)

MI Stable Pnor to IORO (Interrupt Ack_)

I<DNOles:

taem ~ tw{¢lH) + If -65 (75)'

@ lacl" Ic -70 1801"

tca ~ 11/11 ('I>Ll + Ir ·50 (40)'

4 tcaf ~ Iw ('I>Ll + Ir -45 (6Q)"

5 Idem ~ Ie 170 (2101'

6 Idc! '" Iw (¢Ill + Ir -170 (2101'

7 tcdf~ ('~Ll + tr 70 (80)'

8 tVII (MRLl ~ tc 30 (40)"

9 tw (MRH) " tw ('I.H) + If 20 (30)"

~ tw (WRI " Ic -30 (401'

11 Imr"' 2tc + tw I'I-H) + If 65 ISO)"

IC = tw (<I-H) + Iw {'I-Ll + tr + If

tFIC)

'm,

100

®®

80

FROM OUTPUT <>-~----+---I.---i

UNDER TEST

CL 50 pF

Cl- 200pF

Cl ~ 50 pF

CL = 30pF

CL ~ 50 pF

CL" 50pF

Rl + 2.1 k!1

"These values apply to the j.£PD780.

LOAD CIRCUIT FOR OUTPUT

II

371

5 Page

fl-PD780

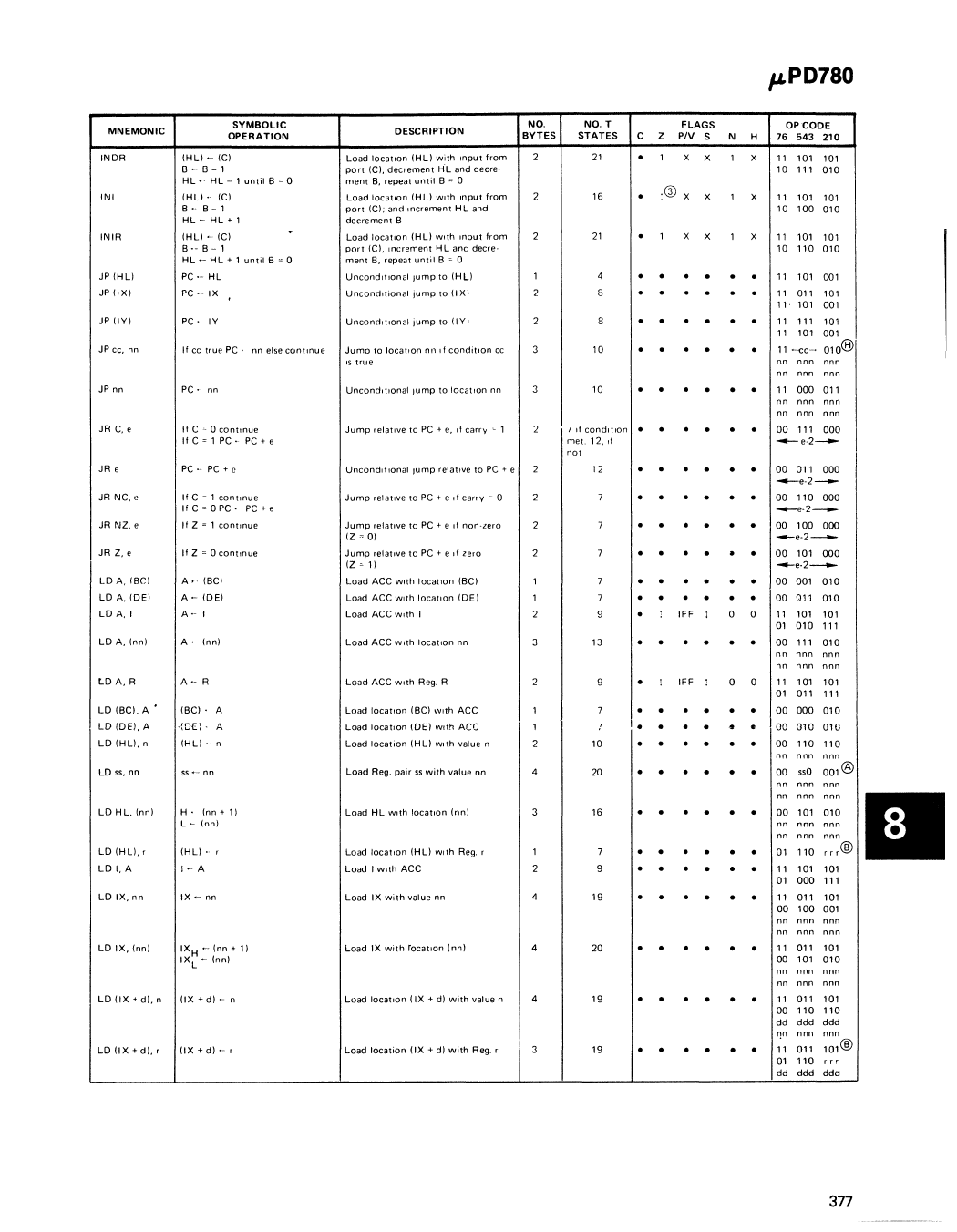

MNEMONIC

INDR

INI

INIR

JP IHLI

JP (IX)

SYMBOLIC

OPERATION

IHLI-ICI

B - B-1

HL·- HL - 1 until B '" 0

IHLI'~ ICI

B- B 1

HL ..... HL + 1

IHLI .~ ICI

.

B·- B-1

HL.- HL + 1 until 8 '" 0

PC·- HL

PC·- IX

JP IIYI

PC· IY

JP ce, nn

If cc true PC • nn else contmue

JP nn

PC· nn

JA C, e

JR e

JR NC, e

JR NZ. e

JR Z. e

LD A. IBel

LD A.IDEI

LD A, I

LD A. (nn)

If C '- 0 continue

If C = 1 PC - PC + e

PC··PC+c

If C = 1 continue

IfC~OPC· PC'" e

If Z = 1 contmue

If Z = 0 continue

A·~ IBCI

A- IDEI

A-I

A 0-- (nn)

LOA. R

A- R

LD IBCI. A •

LD IDEI. A

LD IHLI. n

IBCI· A

·(D£l- A

(HL) .- n

LD 55, nn

55-nn

LD HL. (nn)

LD IHLI.t

LD I. A

LD IX, nn

H· (nn + 11

L - (nn)

(HL) .' r

1- A

IX ..... nn

LD IX, (nn)

IX H <-(nn+ll

IX L .... Inn)

LD (IX of dl, n (IX + d) ..... n

LD IIX +dl. t (IX +d) -- r

DESCRIPTION

NO.

BYTES

Load location fHU with Input from

port Ie}, decrement H"L and deere-

ment B. repeat until B " 0

Load location (HL) with Input from

port Ie); and Increment HL and

decrement B

Load location (HL) with Input from

port Ie)' Increment HL and deere-

ment B. repeat until B =. 0

Unconditional Jump to (HL)

Unconditional jump to (I Xl

2

2

2

1

2

Unconditional jump to (IY)

2

Jump to location nn I f condition cc

IS true

3

Unconditional Jump to location nn

3

Jump relaTIve to PC + e, If carry '- 1

2

Unconditional lump relative to PC + e 2

Jump relative to PC + e d carry" 0

2

Jump relative to PC + e If non·zero

12" 01

Jump relative to PC ... e If zero

IZ'1I

Load ACe with location (BC)

Load ACe with location IDEI

Load Ace with I

2

2

1

1

2

Load ACe with location nn

3

Load ACe with Reg. R

Load location (BC) with ACe

Load location IDE) with ACe

Load location (HU with value n

Load Reg. pair ss with value nn

2

1

1

2

4

Load HL with location (nn)

3

Load location (HLl with Reg. r

Load I with ACe

Load IX with value nn

1

2

4

Load IX with rocatlon (nn)

4

Load IDeation (IX + d) with value n

4

Load location OX + d) with Reg. r

3

NO. T

STATES

21

CZ

·1

FLAGS

P/V S

XX

·16 :@ X X

·21 1 X X

4

8

8

10

··

··

····

··

··

····

10 · · · ·

I' · · · ·7 condition

mel. 12. If

· · · ·not

12

· ·7 · ·

·7 · · ·

7 ····

7

·· · ·7

·· · · ·9 ! IFF 1

·13 · · ·

9 ! IFF !

·7

· · ·7

· ·· · ·

10

·· ·· ·· ··20

16 · · · ·

7

9

19

··· ··· ··· ···

20 · · · ·

19 · · · ·

19 · · · ·

NH

1X

1X

1X

·· ··

··

··

··

··

······ ······

00

··

00

···· ····

··

··· ···

··

··

··

OPCODE

76 543 210

11 101 101

10 111 010

11 101 101

10 100 010

11 101 101

10 110 010

11 101 001

11 011 101

11' 101 001

11 111 101

11 101 001

11 --cc-- 010@

nn nnn nnn

nn nnn nnn

11 000 011

nn nnn nnn

nn nnn nnn

00 111 000

-4-- e-2--.-.

00 011 000

-"-e·2~

00 110 000

~e-2~

00 100 000

~e·2~

00 101 000

........ e·2~

00 001 010

00 Q11 010

11 101 101

01 010 111

00 111 010

nn nnn nnn

nn nnn nnn

11 101 101

01 011 111

00 000 010

00 010 010

00 110 110

nn nnn nnn

00 ssO 001®

nn nnn nnn

nn nnn nnn

00 101 010

nn nnn nnn

nn nnn nnn

01 110 rrr®

11 101 101

01 000 111

11 011 101

00 100 001

nn nnn nnn

nn nnn nnn

11 011 101

00 101 010

nn nnn nnn

nn nnn nnn

11 011 101

00 110 110

dd ddd ddd

~n nnn nnn

11 011 101®

01 110 rrr

dd ddd ddd

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet UPD780.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| UPD780 | 8-BIT N-CHANNEL MICROPROCESSOR | NEC |

| UPD780-1 | 8-BIT N-CHANNEL MICROPROCESSOR | NEC |

| UPD7800 | High End Single Chip 8-Bit Microcomputer | NEC Electronics |

| UPD780016Y | (UPD780016Y / UPD780018Y) 8-Bit Single-Chip Microcontroller | NEC Electronics |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |